User manual CADENCE DESIGN SYSTEMS CADENCE ORCAD FPGA SYSTEM PLANNER DATASHEET

Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets... DON'T FORGET : ALWAYS READ THE USER GUIDE BEFORE BUYING !!!

If this document matches the user guide, instructions manual or user manual, feature sets, schematics you are looking for, download it now. Lastmanuals provides you a fast and easy access to the user manual CADENCE DESIGN SYSTEMS CADENCE ORCAD FPGA SYSTEM PLANNER. We hope that this CADENCE DESIGN SYSTEMS CADENCE ORCAD FPGA SYSTEM PLANNER user guide will be useful to you.

Lastmanuals help download the user guide CADENCE DESIGN SYSTEMS CADENCE ORCAD FPGA SYSTEM PLANNER.

Manual abstract: user guide CADENCE DESIGN SYSTEMS CADENCE ORCAD FPGA SYSTEM PLANNERDATASHEET

Detailed instructions for use are in the User's Guide.

[. . . ] Often the pin assignment for these FPGAs is done manually at a pin-by-pin level in an environment that is unaware of the placement of critical PCB components that are connected to FPGAs. Without BeneFiTS understanding the impact to PCB routing, FPGA-based design projects are forced to · Scalable, cost-effectiveFPGA-PCB choose between two poor options: live co-design solution from OrCAD to with suboptimal pin assignment, which Allegro® GXl can increase the number of layers on a PCB · Shortenstimeforoptimuminitialpin design; or deal with several unnecessary assignment, accelerating PCB design iterations at the tail end of the design cycle. schedules Even with several iterations, this manual and error-prone approach can result in · AcceleratesintegrationofFPGAswith unnecessary PCB design re-spins. [. . . ] Above all, there is no online rules-checking to ensure that the right pin types are being used for the signals that are assigned to the FPGA pins. As a result, users have to make several iterations between the spreadsheet-based tools and the tools from FPGA vendors. Often this adds an increased number of iterations between the PCB layout designer who cannot route the signals from FPGA pins on available layers and the FPGA designer who has to accept paper-based or verbal

Figure 2: Placement/Floorplan view of the OrCAD FPGA System Planner provides users relative placement of critical components for optimum pin assignment synthesis

www. cadence. com

C ADE nCE OrCAD FPGA Sy STE m PlAnn Er

2

FPGA Vendor Tools

OrCAD FPGA System Planner

OrCAD Capture/CIS

OrCAD PCB Designer

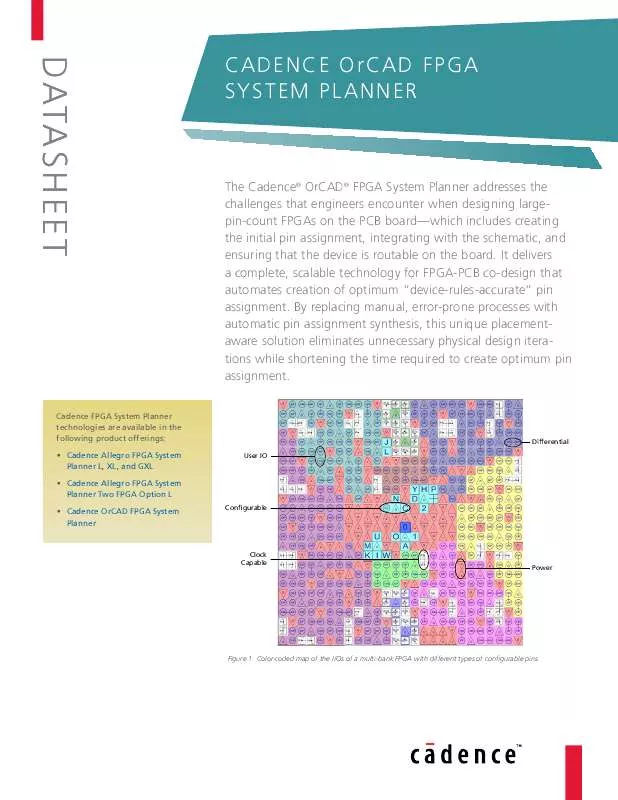

module or between two FPGAs. The OrCAD FPGA System Planner understands differential signals, and power signals, as well as clock signals.

FPGA DeViCe ruLeS

The OrCAD FPGA System Planner comes with a library of device-accurate FPGA models that incorporate pin assignment rules and electrical rules specified by FPGA device vendors. These FPGA models are used by the synthesis engine to ensure that the vendor-defined electrical usage rules of the FPGAs are strictly adhered to. These rules dictate such things as clock and clock region selection, bank allocation, SSO budgeting, buffer driver utilization, I/O standard voltage reference levels, etc. During synthesis, the OrCAD FPGA System Planner automatically checks hundreds of combinations of these rules to ensure that the FPGA pins are optimally and accurately utilized.

OrCAD Part Library Symbols, Footprints

Figure 3: The OrCAD FPGA System Planner uses symbols and footprints from existing libraries

pin-assignment suggestions from the PCB layout designer. Once a change is made to the pin assignment by the FPGA designer, the pin assignment change has to be made in the schematic design by the hardware designer. Such iterations add several days if not weeks to the design cycle and possibly a great deal of frustration for the team members. Since this is a manual process, mistakes that are not detected can also cause expensive physical prototype iterations. While it may help to automate the synchronization of changes made to the pin assignment by the FPGA designer, hardware designer, or PCB layout designer, it doesn't reduce the root cause of these iterations. Pin assignment that is not guided by all three aspects--FPGA resource availability, FPGA vendor pin assignment rules, and routability of FPGA pins on a PCB--requires many iterations at the tail end of the design process, thereby extending the time it takes to integrate today's complex, large-pin-count FPGAs on a PCB.

The OrCAD FPGA System Planner allows users to specify connectivity between components within the FPGA sub-system at a higher level through interface definitions. Users can create interfaces such as DDR2, DDR3, and PCI Express, and use these to specify connectivity between an FPGA and a memory DIMM

SPeCiFYinG DeSiGn inTenT

The OrCAD FPGA System Planner comes with an FPGA device library to help with selection of devices to be placed. It uses OrCAD PCB Editor footprints for the floorplan view and allows users to quickly create relative placement of the FPGA system components.

Figure 4: OrCAD FPGA System Planner optimization

www. cadence. com

C ADE nCE OrCAD FPGA Sy STE m PlAnn Er

3

PLACeMenT AWAre Pin ASSiGnMenT SYnTHeSiS

The OrCAD FPGA System Planner provides users a way to create an FPGA system placement view using OrCAD PCB footprints. Users specify connectivity between components in the placement view and the FPGA at a high level using interfaces such as DDRx, PCI Express, SATA, Front Side Bus, etc. that connect FPGAs and other components in the design, shortening the time to specify design intent for the FPGA system. [. . . ] Suitable for companies that use FPGAs to prototype ASICs · AllegroFPGASystemPlannerXL--for concurrent pin assignment, synthesis, and post-placement optimization of up to four FPGAs at a time · AllegroFPGASystemPlannerL--forpin assignment synthesis and post-placement optimization of a single FPGA · OrCADFPGASystemPlanner--for optimum initial pin assignment synthesis of a single FPGA.

SALeS, TeCHniCAL SuPPOrT, AnD TrAininG

The OrCAD product line is owned by Cadence Design Systems, Inc. , and supported by a worldwide network of Cadence Channel Partners (VARs). For sales, technical support, or training, contact your local Cadence Channel Partner. For a complete list of authorized Cadence Channel Partners, visit www. cadence. com/Alliances/channel_ partner.

© 2009 Cadence Design Systems, inc. [. . . ]

DISCLAIMER TO DOWNLOAD THE USER GUIDE CADENCE DESIGN SYSTEMS CADENCE ORCAD FPGA SYSTEM PLANNER Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets...manual CADENCE DESIGN SYSTEMS CADENCE ORCAD FPGA SYSTEM PLANNER