Detailed instructions for use are in the User's Guide.

[. . . ] The environment features integrated IC/package I/O planning capabilities and three dimensional (3D) die stack creation and editing capabilities. In addition, full online design-rule checking (DRC) supports the complex and unique requirements of all combinations of laminate, ceramic, and deposited substrate technologies. Multilayer flip-chip along with radial any-angle routing provide rapid constraint-driven interconnect creation.

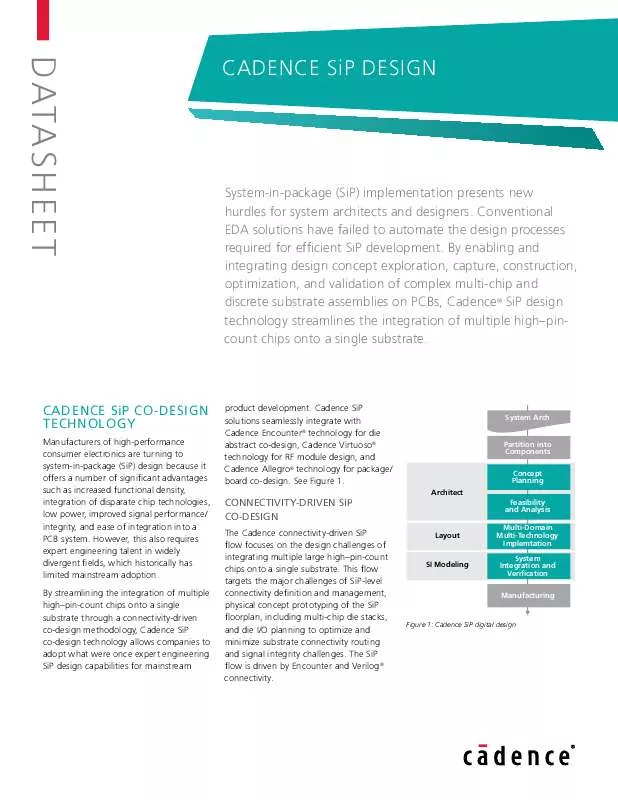

Cadence SiP Digital SI

SiP Digital SI provides an environment for the co-simulation of SiP interconnect, including embedded ICs and the target PCB. [. . . ] For RF/ analogICsdesignedwithVirtuosoLayout Editor, SiPRFArchitectXLcanexport a design-ready SiP die footprint that includes post-wafer processing geometry adjustments.

· Automatescircuitsimulation testbench management and parasitic backannotation from Cadence SiP LayoutwiththeChipIntegrationOption

Cadence SiP Layout/Chip Integration Option

SiPLayoutwiththeChipIntegration Option provides a complete Virtuoso schematic connectivity-driven package substrate layout environment for SiP RF module physical design. It features integrated I/O planning co-design capabilities (for digital ICs) and 3D diestack creation and editing. It supports all packaging methods including PgA, BgA, micro-BgA, chip scale, flip-chip, andwirebondattach. SiPLayout/Chip Integration Option is based on a co-design process that manages physical, electrical, and manufacturing interfaces between design components--across all associated design fabrics--allowing designers to make tradeoffs and optimize the entire system interconnect. Full online and batch design-rule checking (DRC) supports the complex and unique requirements of all combinations of laminate, ceramic, and deposited substrate technologies. SiPLayout/ChipIntegrationOptionalso supports multiple cavities, complex shapes, and interactive and automatic wirebonding.

Benefits

· Providesasingle, top-levelVirtuoso schematic- and simulation-driven environment for RF ICs, SiP RF module substrate, and embedded RF passive elements · Supportsbi-directionalECOandLVS flow between RF/AMS IC design team and SiP RF module layout team · Supportssubstrate-levelRFpassive parameterized cell (Pcell) creation via Virtuoso top-level design definition · SpeedsdesignwithdirectexportofSiP substrate-ready IC die footprints from VirtuosoLayoutEditor

Cadence SiP RF Architect XL

SiPRFArchitectXLprovidesthe integration and flow environment between the Virtuoso Analog Design Environment(and/orVirtuosoLayout Suite)andCadenceSiPLayoutwiththe Chip Integration Option. It enables the creation of a single, circuit simulationcapable, top-level SiP RF module schematic that includes the RF/analog ICs required for the final SiP design. SiP RFArchitectXLprovidesschematic-level pre layout definition and characterization

www. ca de nce . com

CADEnCE SiP DESIgn

3

Benefits

· Providesbi-directionalECOandLVS flow between RF design team and SiP RF module layout team · Supportssubstrate-levelRFpassivePcell creation through Virtuoso top level driven design · AllowsdirectimportofSiPsubstrateready IC die footprints from Virtuoso LayoutEditor · Speedsdiestackassemblyand optimization with 3D creation/editing · OptimizesICI/Opadring/array co-design and connectivity at IC, substrate, and system levels · Minimizeslayerusagebyoptimizing SI and routability-driven connectivity assignment between ICs and substrate · Reducestedious, time-consuming manual breakout editing via flip-chip die autoroute breakout · Constraint-drivenHDIdesignwith automation-assisted interactive routing enables greater design miniaturization, speeds implementation, and reduces potential errors · IncludescomprehensivesubstrateDFM capabilities for rapid manufacturing preparation · IncludestheCadence3DDesignViewer and DRC for accurate, full 3D wire bondability verification, design review debug, and design documentation for assembly and test

thecompletedSiP. EmbeddedLVSroutines and ECO management capabilities ensure that the logical SiP definition matches the physical SiP implementation, including any ICs that are partitioned and co-designed as part of the SiP.

ring and bump matrix within the context of the SiP substrate editing canvass. The I/O planner is based on Encounter technology, ensuring it is 100 percent compatible with the chip design team's IC tools and provides complete IC technology file compliance. Note: This feature is not available on Windows (Linux / Unix only).

Figure 8: 3D die stack editor Figure 10: Embedded signal integrity simulation

3D DESIGN VIEWER

The Cadence 3D Design Viewer is a full, solid model 3D viewer and 3D wirebond DRC solution for complex IC package designs. It allows users to visualize and investigate an entire design, or a selected design subset such as a die stack or complex via array. It also provides a common reference point for cross-team design reviews.

SUBSTRATE FLOORPLANNER

The floorplanner allows the physical prototyping and evaluation of various substrate-level SiP implementation concepts. It provides a full rules-driven, connectivity-based capability that ensures a correct-by-construction approach. The die abstracts, discrete components, and connectivity and constraint data is used to build the physical SiP implementation. The SiP architect can then use the graphical, intuitive editing tools to construct and evaluate critical sections of the design.

PACKAGE MODELING FOR SYSTEM-LEVEL ANALYSIS

CreationofIBIS, RLC, orCadence DMLinterconnectmodelsiseasily accomplished, either for a selected set of nets or for the entire package. Design teams can then easily reuse these models at the system level to ensure that package effects are properly considered when optimizing PCB cost/performance tradeoffs.

POWER DELIVERY NETWORK DESIGN FOR LOW POWER

An integrated analysis environment enables sufficient, efficient, and stable power delivery network design through the optimization of the package impedance profile and minimizes power supply voltage ripple.

Figure 9: 3D design viewer

EMBEDDED INTEGRATION WITH THIRD-PARTY 3D FIELD SOLVERS

Figure 7: Substrate floorplanner

INTEGRATED CONSTRAINT MANAGEMENT

The spreadsheet-based integrated constraint management system provides the definition, application, and management of interconnect constraints and topologies at the physical prototyping and implementation level. Designers can import constraints and apply them to industry-standard bus protocols--such as PCI Express and DDR2--through hierarchical interconnect topology templates that are available from Cadence as well as various IC vendors. (See Figure 11. )

3D DIE STACK EDITOR

The die stack editor provides a 3D construction environment for assembling complex die stacks that can include spacers, interposers, and die-attach methods such as wirebond and flip-chip.

Seamless integration with third-party supplied quasi-static and full-wave field solver engines combined with SPICEbased simulation engines--all accessed directly from within the physical SiP design environment--enable modeling and simulation of package interconnect without the time-consuming setup of standalone point tools. Engineers can quickly check tradeoffs to the physical design to ensure that electrical requirements are not compromised. [. . . ] The package layout designer can then use intuitive graphical editing tools to implement the design and prepare it for manufacturing. It also supports all packaging methods: PgA, LGA, BGA, micro-BGA, andchipscale, as well as flip-chip and wirebond attach methods. An embedded, push-button, full 3D quasi-static field solver enables the extraction and creation of detailed, accurategeometricRLCorS-Parameter package simulation models for use during PCB design.

FLOW INTEGRATION WITH VIRTUOSO LAYOUT EDITOR

SiPRFArchitectXLprovidesasingle, integrated design flow built around the Virtuoso DFII framework. [. . . ]