Detailed instructions for use are in the User's Guide.

[. . . ] Intel® Celeron® Processor up to 1. 10 GHz

Datasheet

s

s

s

s s s

s

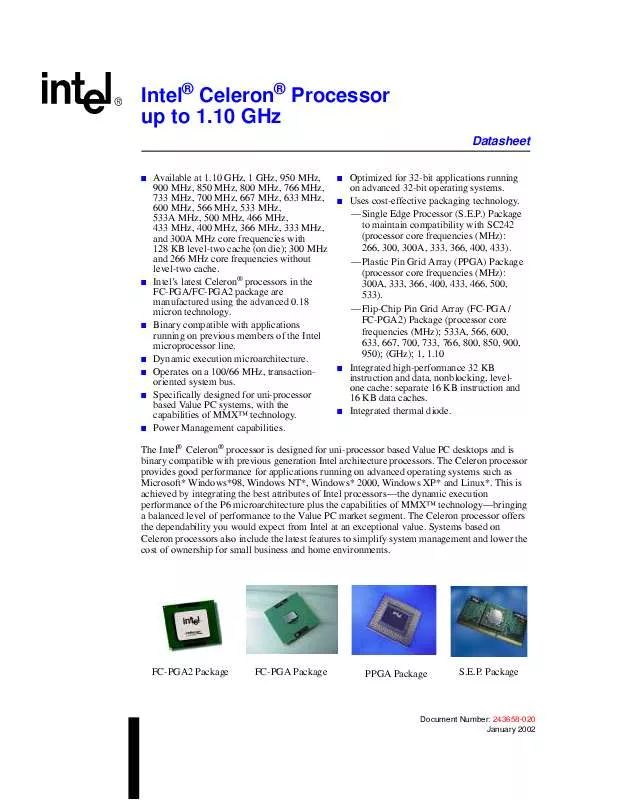

Available at 1. 10 GHz, 1 GHz, 950 MHz, 900 MHz, 850 MHz, 800 MHz, 766 MHz, 733 MHz, 700 MHz, 667 MHz, 633 MHz, 600 MHz, 566 MHz, 533 MHz, 533A MHz, 500 MHz, 466 MHz, 433 MHz, 400 MHz, 366 MHz, 333 MHz, and 300A MHz core frequencies with 128 KB level-two cache (on die); 300 MHz and 266 MHz core frequencies without level-two cache. Intel's latest Celeron® processors in the FC-PGA/FC-PGA2 package are manufactured using the advanced 0. 18 micron technology. Binary compatible with applications running on previous members of the Intel microprocessor line. Operates on a 100/66 MHz, transactionoriented system bus. [. . . ] All APIC I/O signal timings are referenced at 1. 25 V for S. E. P. and PPGA packages and 0. 75 V for the FC-PGA/FC-PGA2 packages at the processor edge fingers. All AC timings for the TAP signals at the processor edge fingers are referenced to the TCK rising edge at 0. 70 V for S. E. P. and PPGA packages and 0. 75 V for the FC-PGA/FC-PGA2 packages. All TAP signal timings (TMS, TDI, etc. ) are referenced at 1. 25 V for S. E. P. and PPGA packages and 0. 75 V for the FC-PGA/FC-PGA2 packages at the processor edge fingers.

Figure 2. BCLK to Core Logic Offset

BCLK at Edge Fingers T1B' BCLK at Core Logic 1. 25V

0. 5V

48

Datasheet

Intel® Celeron® Processor up to 1. 10 GHz

Figure 3. BCLK*, PICCLK, and TCK Generic Clock Waveform

th tr 1. 7V (2. 0V*) CLK 0. 7V (0. 5V*) tf tl tp 1. 25V

Tr Tf Th Tl Tp

= = = = =

T5, T6, T3, T4, T1,

T25, T26, T23, T24, T22,

T34 T35 T32 T33 T31

(Rise Tim e) (Fall Tim e) (High Tim e) (Low Time) (BLCK, TCK, PICCLK Period)

Note: BCLK is referenced to 0. 5 V and 2. 0 V. PICCLK is referenced to 0. 7 V and 1. 7 V. and PPGA packages, TCK is referenced to 0. 7 V and 1. 7 V. For the FC-PGA package, TCK is referenced to V REF ±200m V.

Figure 4. System Bus Valid Delay Timings

CLK Tx V Valid Tpw Tx = T7, T11, T29a, T29b (Valid Delay) Tpw = T14, T14B, T15 (Pulse Width) V = 1. 0V for AGTL+ signal group; For S. E. P and PPGA packages, 1. 25V for CMOS, APIC and JTAG signal groups For FC-PGA package, 0. 75V for CMOS, APIC and TAP signal groups Valid Tx

Signal

Figure 5. System Bus Setup and Hold Timings

CLK Ts V Th Valid

Signal

Ts = T8, T12, T27 (Setup Time) Th = T9, T13, T28 (Hold Time) V = 1. 0V for AGTL+ signal group; For S. E. P. and PPGA packages, 1. 25V for APIC and JTAG signal groups For the FC-PGA package, 0. 75V for APIC and TAP signal groups

Datasheet

49

Intel® Celeron® Processor up to 1. 10 GHz

Figure 6. System Bus Reset and Configuration Timings (For the S. E. P. and PPGA Packages)

BCLK Tu Tt RESET# Tv Tw Valid Tt Tu Tv Tw Tx = T9 (AGTL+ Input Hold Time) = T8 (AGTL+ Input Setup Time) = T10 (RESET# Pulse Width) = T16 (Reset Configuration Signals (A[14:5]#, BR0#, FLUSH#, INIT#) Setup Time) = T17 (Reset Configuration Signals (A[14:5]#, BR0#, FLUSH#, INIT#) Hold Time) Tx

Configuration (A[14:5]#, BR0#, FLUSH#, INT#)

Figure 7. System Bus Reset and Configuration Timings (For the FC-PGA/FC-PGA2 Package)

BCLK Tu Tt RESET# Tv Configuration (A20M#, IGNNE#, LINT[1:0]) Configuration (A[14:5]#, BR0#, FLUSH#, INT#) Tt Tu Tv Tw Tx Ty Safe Tw Valid = T9 (AGTL+ Input Hold Time) = T8 (AGTL+ Input Setup Time) = T10 (RESET# Pulse Width) = T16 (Reset Configuration Signals (A[14:5]#, BR0#, FLUSH#, INIT#) Setup Time) = T17 (Reset Configuration Signals (A[14:5]#, BR0#, FLUSH#, INIT#) Hold Time) T20 (Reset Configuration Signals (A20M#, IGNNE#, LINT[1:0]) Hold Time) Ty = T19 (Reset Configuration Signals (A20M#, IGNNE#, LINT[1:0]) Delay Time) Tz = T18 (Reset Configuration Signals (A20M#, IGNNE#, LINT[1:0]) Setup Time) Tz Valid Tx

50

Datasheet

Intel® Celeron® Processor up to 1. 10 GHz

Figure 8. Power-On Reset and Configuration Timings

BCLK VccCORE, VTT, VREF

PWRGOOD Ta RESET#

VIL, max

VIH, min Tb

TC Configuration (A20M#, IGNNE#, INTR, NMI) Ta Tb Tc Valid Ratio = T15 (PWRGOOD Inactive Pulse) = T10 (RESET# Pulse Width) = T20 (Reset Configuration Signals (A20M#, IGNNE#, LINT[1:0]) Hold Time) (FC-PGA)

Figure 9. Test Timings (TAP Connection)

TCK

1. 25V Tv Tw

TDI, TMS

1. 25V Tr Ts

Input Signals

Tx

TDO

Tu

Ty

Output Signals

Tz

Tr = T43 (All Non-Test Inputs Setup Time) Ts = T44 (All Non-Test Inputs Hold Time) Tu = T40 (TDO Float Delay) Tv = T37 (TDI, TMS Setup Time) Tw = T38 (TDI, TMS Hold Time) Tx = T39 (TDO Valid Delay) Ty = T41 (All Non-Test Outputs Valid Delay) Tz = T42 (All Non-Test Outputs Float Delay)

Figure 10. Test Reset Timings

TRST# 1. 25V Tq Tq = T37 (TRST# Pulse Width)

C

Datasheet

51

Intel® Celeron® Processor up to 1. 10 GHz

3. 0

System Bus Signal Simulations

Signals driven on the Celeron processor system bus should meet signal quality specifications to ensure that the components read data properly and to ensure that incoming signals do not affect the long term reliability of the component. Specifications are provided for simulation at the processor core; guidelines are provided for correlation to the processor edge fingers. These edge finger guidelines are intended for use during testing and measurement of system signal integrity. [. . . ] The supply for VCC1. 5 must be the same one used to supply VTT. The VCCCMOS pin provides the CMOS voltage for use by the platform. The 2. 5 V must be provided to the VCC2. 5 input and 1. 5 V must be provided to the VCC1. 5 input. The processor re-routes the 2. 5 V input to the VCCCMOS output via the package. [. . . ]