User manual KINGSTON KVR667D2Q8F54GHE MEMORY MODULE SPECIFICATIONS

Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets... DON'T FORGET : ALWAYS READ THE USER GUIDE BEFORE BUYING !!!

If this document matches the user guide, instructions manual or user manual, feature sets, schematics you are looking for, download it now. Lastmanuals provides you a fast and easy access to the user manual KINGSTON KVR667D2Q8F54GHE. We hope that this KINGSTON KVR667D2Q8F54GHE user guide will be useful to you.

Lastmanuals help download the user guide KINGSTON KVR667D2Q8F54GHE.

Manual abstract: user guide KINGSTON KVR667D2Q8F54GHEMEMORY MODULE SPECIFICATIONS

Detailed instructions for use are in the User's Guide.

[. . . ] Memory Module Specifications

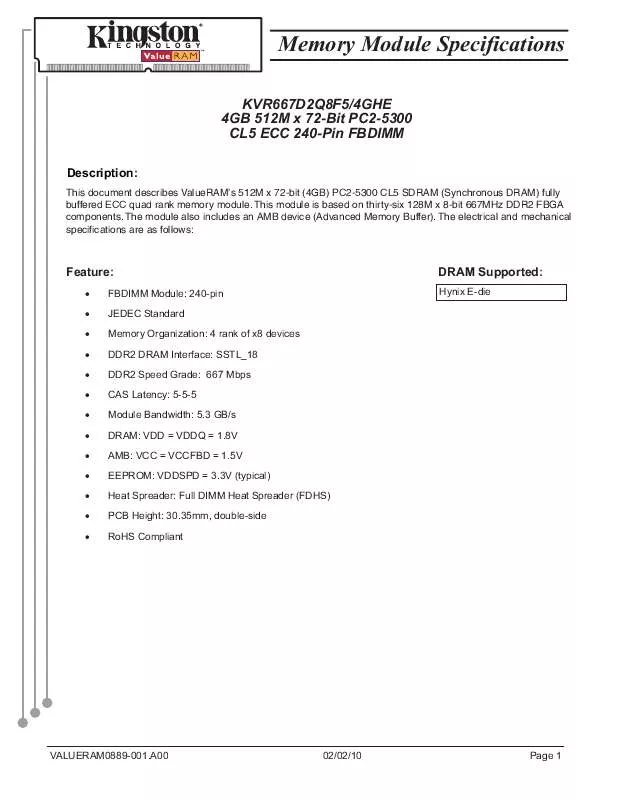

KVR667D2Q8F5/4GHE 4GB 512M x 72-Bit PC2-5300 CL5 ECC 240-Pin FBDIMM

Description:

This document describes ValueRAM's 512M x 72-bit (4GB) PC2-5300 CL5 SDRAM (Synchronous DRAM) fully buffered ECC quad rank memory module. [. . . ] System Clock Signals SCK and SCK switch at one half the DRAM CK/CK frequency 2. Eight pins reserved for forwarded clocks, eight pins reserved for future architecture flexibility

Absolute Maximum Ratings

Symbol VIN, VOUT VCC VDD VTT TSTG TCASE Parameter Voltage on any pin relative to V Voltage V DD pin relative to Vss Voltage on V TT pin relative to V SS Storage temperature DDR2 SDRAM device operat ing temperature (Ambient) AMB device operating temperature (Ambient)

SS

MIN -0. 3 -0. 3 -0. 5 -0. 5 -55 0 0

MAX 1. 75 1. 75 2. 3 2. 3 100 95 (1) 110

Units V V V V °C °C °C

Voltage on V CC pin relative to V SS

Note: (1) Above 85°C DRAM case temperature the Auto-Refresh command interval has to be reduced to tREFI = 3. 9 µs.

VALUERAM0889-001. A00

Page 3

TECHNOLOGY

Functional Block Diagram:

S3 S2 S1 S0 DQS0 DQS0 DQS9 DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQS1 DQS1 DQS10

DM/ NU/ RDQS RDQS CS DQS DQS DM/ NU/ RDQS RDQS CS DQS DQS DM/ NU/ RDQS RDQS CS DQS DQS

DQS4 DQS4 DQS13 I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ RDQS RDQS CS DQS DQS

D0

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D9

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D18

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

D27

DQ32 DQ33 DQ34 DQ35 DQ36 DQ37 DQ38 DQ39

DQS5 DQS14

DM/ NU/ RDQS RDQS CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ RDQS RDQS CS DQS DQS

D4

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D13

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D22

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

D31

DQS5

DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 DQS2 DQS2 DQS11

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

D1

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D10

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D19

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

D28

DQ40 DQ41 DQ42 DQ43 DQ44 DQ45 DQ46 DQ47 DQS6 DQS6 DQS15

DM/ NU/ RDQS RDQS CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ RDQS RDQS CS DQS DQS

D5

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D14

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D23

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

D32

DQ16 DQ17 DQ18 DQ19 DQ20 DQ21 DQ22 DQ23 DQS3 DQS3 DQS12 DQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31

DM/ NU/ RDQS RDQS CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ RDQS RDQS CS DQS DQS

D2

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D11

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D20

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

D29

DQ48 DQ49 DQ50 DQ51 DQ52 DQ53 DQ54 DQ55 DQS7 DQS7 DQS16

DM/ NU/ RDQS RDQS CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ RDQS RDQS CS DQS DQS

D6

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D15

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D24

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

D33

DM/ NU/ RDQS RDQS CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ RDQS RDQS CS DQS DQS

D3

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D12

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D21

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

D30

DQ56 DQ57 DQ58 DQ59 DQ60 DQ61 DQ62 DQ63 DQS8 DQS8 DQS17 CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7

DM/ NU/ RDQS RDQS CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ RDQS RDQS CS DQS DQS

D7

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D16

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D25

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

D34

DM/ NU/ RDQS RDQS CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ RDQS RDQS CS DQS DQS

D8

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D17

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

DM/ NU/ CS DQS DQS RDQS RDQS

D26

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

D35

PN0-PN13 PN0-PN13 PS0-PS9 PS0-PS9

SN0-SN13 SN0-SN13 SS0-SS9 SS0-SS9

A M B

SCL SDA SA1-SA2 SA0 RESET SCK/SCK

S0 -> CS (D0-D8) / S2 -> CS (D18-D26) CKE0 -> CKE (D0-D8 / D18-D26) S1 -> CS (D9-D17) / S3 -> CS (D27-D35) CKE1 -> CKE (D9-D17 / D27-D35) ODT -> ODT (all SDRAMs) BA0-BA2 (all SDRAMs) A0-A15 (all SDRAMs) RAS (all SDRAMs) CAS (all SDRAMs) WE (all SDRAMs) CK/CK (all SDRAMs)

VTT VCC VDDSPD

22

Terminators AMB SPD, AMB D0-D35, AMB D0-D35 D0-D35, SPD, AMB

825

VDD VTT VREF VSS

Notes: 1. DQ-to-I/O wiring may be changed within a byte. There are two physical copies of each

address/command/control/clock

All address/command/control/clock

Serial PD SCL WP A0 A1 A2 SA0 SA1 SA2

SDA

VALUERAM0889-001. A00

Page 4

TECHNOLOGY

Architecture:

Advanced Memory Buffer Pin Description:

Pin Name Pin Description Count

FB-DIMM Channel Signals

SCK SCK PN[13:0] PN[13:0] PS[9:0] PS[9:0] SN[13:0] SN[13:0] SS[9:0] SS[9:0] FBDRES System Clock Input, positive line System Clock Input, negative line Primary Northbound Data, positive lines Primary Northbound Data, negative lines Primary Southbound Data, positive lines Primary Southbound Data, negative lines Secondary Northbound Data, positive lines Secondary Northbound Data, negative lines Secondary Southbound Data, positive lines Secondary Southbound Data, negative lines To an external precision calibration resistor connected to Vcc

99

1 1 14 14 10 10 14 14 10 10 1

DDR2 Interface Signals

DQS[8:0] DQS[8:0] DQS[17:9]/DM[8:0] DQS[17:9] DQ[63:0] CB[7:0] A[15:0]A, A[15:0]B BA[2:0]A, BA[2:0]B RASA, RASB CASA, CASB WEA, WEB ODTA, ODTB CS[1:0]A, CS[1:0]B CLK[3:0] CLK[3:0] DDRC_C14 DDRC_B18 DDRC_C18 DDRC_B12 DDRC_C12 Data Strobes, positive lines Data Strobes, negative lines Data Strobes (x4 DRAM only), positive lines. These signals are driven low to x8 DRAM on writes. Data Strobes (x4 DRAM only), negative lines Data Checkbits Addresses. A10 is part of the pre-charge command Bank Addresses Part of command, with CAS, WE, and CS[3:0]. Part of command, with RAS, WE, and CS[3:0]. [. . . ] Leave floating on the DIMM Tie to ground on the DIMM AMB reset signal No connect. [. . . ]

DISCLAIMER TO DOWNLOAD THE USER GUIDE KINGSTON KVR667D2Q8F54GHE Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets...manual KINGSTON KVR667D2Q8F54GHE