User manual TEXAS INSTRUMENTS AM1810 ARM MICROPROCESSOR FEATURES FOR PROFIBUS 11-2010

Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets... DON'T FORGET : ALWAYS READ THE USER GUIDE BEFORE BUYING !!!

If this document matches the user guide, instructions manual or user manual, feature sets, schematics you are looking for, download it now. Lastmanuals provides you a fast and easy access to the user manual TEXAS INSTRUMENTS AM1810 ARM MICROPROCESSOR. We hope that this TEXAS INSTRUMENTS AM1810 ARM MICROPROCESSOR user guide will be useful to you.

Lastmanuals help download the user guide TEXAS INSTRUMENTS AM1810 ARM MICROPROCESSOR.

Manual abstract: user guide TEXAS INSTRUMENTS AM1810 ARM MICROPROCESSORFEATURES FOR PROFIBUS 11-2010

Detailed instructions for use are in the User's Guide.

[. . . ] AM1810

www. ti. com SPRS709 NOVEMBER 2010

AM1810 ARM Microprocessor For PROFIBUS

Check for Samples: AM1810

1 AM1810 ARM Microprocessor

1. 1

12

Features

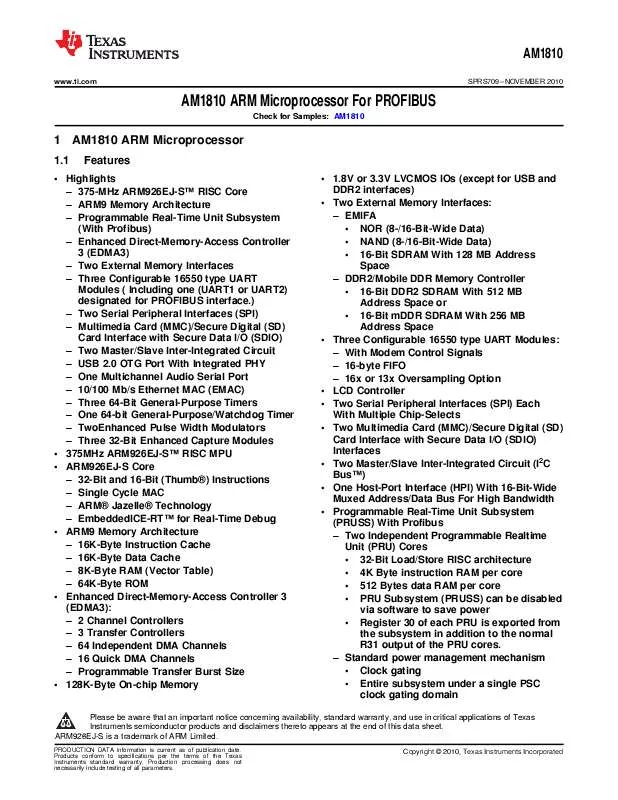

· 1. 8V or 3. 3V LVCMOS IOs (except for USB and DDR2 interfaces) · Two External Memory Interfaces: EMIFA · NOR (8-/16-Bit-Wide Data) · NAND (8-/16-Bit-Wide Data) · 16-Bit SDRAM With 128 MB Address Space DDR2/Mobile DDR Memory Controller · 16-Bit DDR2 SDRAM With 512 MB Address Space or · 16-Bit mDDR SDRAM With 256 MB Address Space · Three Configurable 16550 type UART Modules: With Modem Control Signals 16-byte FIFO 16x or 13x Oversampling Option · LCD Controller · Two Serial Peripheral Interfaces (SPI) Each With Multiple Chip-Selects · Two Multimedia Card (MMC)/Secure Digital (SD) Card Interface with Secure Data I/O (SDIO) Interfaces · Two Master/Slave Inter-Integrated Circuit (I2C BusTM) · One Host-Port Interface (HPI) With 16-Bit-Wide Muxed Address/Data Bus For High Bandwidth · Programmable Real-Time Unit Subsystem (PRUSS) With Profibus Two Independent Programmable Realtime Unit (PRU) Cores · 32-Bit Load/Store RISC architecture · 4K Byte instruction RAM per core · 512 Bytes data RAM per core · PRU Subsystem (PRUSS) can be disabled via software to save power · Register 30 of each PRU is exported from the subsystem in addition to the normal R31 output of the PRU cores. Standard power management mechanism · Clock gating · Entire subsystem under a single PSC clock gating domain

· Highlights 375-MHz ARM926EJ-STM RISC Core ARM9 Memory Architecture Programmable Real-Time Unit Subsystem (With Profibus) Enhanced Direct-Memory-Access Controller 3 (EDMA3) Two External Memory Interfaces Three Configurable 16550 type UART Modules ( Including one (UART1 or UART2) designated for PROFIBUS interface. ) Two Serial Peripheral Interfaces (SPI) Multimedia Card (MMC)/Secure Digital (SD) Card Interface with Secure Data I/O (SDIO) Two Master/Slave Inter-Integrated Circuit USB 2. 0 OTG Port With Integrated PHY One Multichannel Audio Serial Port 10/100 Mb/s Ethernet MAC (EMAC) Three 64-Bit General-Purpose Timers One 64-bit General-Purpose/Watchdog Timer TwoEnhanced Pulse Width Modulators Three 32-Bit Enhanced Capture Modules · 375MHz ARM926EJ-STM RISC MPU · ARM926EJ-S Core 32-Bit and 16-Bit (Thumb®) Instructions Single Cycle MAC ARM® Jazelle® Technology EmbeddedICE-RTTM for Real-Time Debug · ARM9 Memory Architecture 16K-Byte Instruction Cache 16K-Byte Data Cache 8K-Byte RAM (Vector Table) 64K-Byte ROM · Enhanced Direct-Memory-Access Controller 3 (EDMA3): 2 Channel Controllers 3 Transfer Controllers 64 Independent DMA Channels 16 Quick DMA Channels Programmable Transfer Burst Size · 128K-Byte On-chip Memory

1

2

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. ARM926EJ-S is a trademark of ARM Limited.

Copyright © 2010, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. [. . . ] The device MMC/SD Controller does not support SPI mode.

5. 13. 2

MMCSD Peripheral Register Description(s)

Table 5-39. Multimedia Card/Secure Digital (MMC/SD) Card Controller Registers

MMCSD0 BYTE ADDRESS 0x01C4 0000 0x01C4 0004 0x01C4 0008 0x01C4 000C 0x01C4 0010 0x01C4 0014 0x01C4 0018 0x01C4 001C 0x01C4 0020 0x01C4 0024 0x01C4 0028 0x01C4 002C 0x01C4 0030 0x01C4 0034 0x01C4 0038 0x01C4 003C 0x01C4 0040 0x01C4 0044 0x01C4 0048 0x01C4 0050 0x01C4 0064 0x01C4 0068 0x01C4 006C 0x01C4 0070 0x01C4 0074

MMCSD1 BYTE ADDRESS 0x01E1 B000 0x01E1 B004 0x01E1 B008 0x01E1 B00C 0x01E1 B010 0x01E1 B014 0x01E1 B018 0x01E1 B01C 0x01E1 B020 0x01E1 B024 0x01E1 B028 0x01E1 B02C 0x01E1 B030 0x01E1 B034 0x01E1 B038 0x01E1 B03C 0x01E1 B040 0x01E1 B044 0x01E1 B048 0x01E1 B050 0x01E1 B064 0x01E1 B068 0x01E1 B06C 0x01E1 B070 0x01E1 B074

ACRONYM MMCCTL MMCCLK MMCST0 MMCST1 MMCIM MMCTOR MMCTOD MMCBLEN MMCNBLK MMCNBLC MMCDRR MMCDXR MMCCMD MMCARGHL MMCRSP01 MMCRSP23 MMCRSP45 MMCRSP67 MMCDRSP MMCCIDX SDIOCTL SDIOST0 SDIOIEN SDIOIST MMCFIFOCTL MMC Control Register

REGISTER DESCSRIPTION

MMC Memory Clock Control Register MMC Status Register 0 MMC Status Register 1 MMC Interrupt Mask Register MMC Response Time-Out Register MMC Data Read Time-Out Register MMC Block Length Register MMC Number of Blocks Register MMC Number of Blocks Counter Register MMC Data Receive Register MMC Data Transmit Register MMC Command Register MMC Argument Register MMC Response Register 0 and 1 MMC Response Register 2 and 3 MMC Response Register 4 and 5 MMC Response Register 6 and 7 MMC Data Response Register MMC Command Index Register SDIO Control Register SDIO Status Register 0 SDIO Interrupt Enable Register SDIO Interrupt Status Register MMC FIFO Control Register

124

Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): AM1810

Copyright © 2010, Texas Instruments Incorporated

AM1810

www. ti. com SPRS709 NOVEMBER 2010

5. 13. 3 MMC/SD Electrical Data/Timing

Table 5-40 through Table 5-41 assume testing over recommended operating conditions. Timing Requirements for MMC/SD (see Figure 5-25 and Figure 5-27)

NO. 1 2 3 4 PARAMETER tsu(CMDV-CLKH) Setup time, MMCSD_CMD valid before MMCSD_CLK high th(CLKH-CMDV) tsu(DATV-CLKH) th(CLKH-DATV) Hold time, MMCSD_CMD valid after MMCSD_CLK high Setup time, MMCSD_DATx valid before MMCSD_CLK high Hold time, MMCSD_DATx valid after MMCSD_CLK high 1. 2V MIN 4 2. 5 4. 5 2. 5 MAX 4 2. 5 5 2. 5 1. 1V MIN MAX 6 2. 5 6 2. 5 1. 0V MIN MAX UNIT ns ns ns ns

Table 5-41. Switching Characteristics for MMC/SD (see Figure 5-24 through Figure 5-27)

NO. 7 8 9 10 11 12 13 14 f(CLK) f(CLK_ID) tW(CLKL) tW(CLKH) tr(CLK) tf(CLK) td(CLKL-CMD) td(CLKL-DAT) PARAMETER Operating frequency, MMCSD_CLK Identification mode frequency, MMCSD_CLK Pulse width, MMCSD_CLK low Pulse width, MMCSD_CLK high Rise time, MMCSD_CLK Fall time, MMCSD_CLK Delay time, MMCSD_CLK low to MMCSD_CMD transition Delay time, MMCSD_CLK low to MMCSD_DATx transition -4 -4 1. 2V MIN 0 0 6. 5 6. 5 3 3 2. 5 3. 3 -4 -4 MAX 52 400 0 0 6. 5 6. 5 3 3 3 3. 5 -4 -4 1. 1V MIN MAX 50 400 0 0 10 10 10 10 4 4 1. 0V MIN MAX 25 400 UNIT MHz KHz ns ns ns ns ns ns

Copyright © 2010, Texas Instruments Incorporated

Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): AM1810

125

AM1810

SPRS709 NOVEMBER 2010 www. ti. com

10 7 MMCSD_CLK 13 MMCSD_CMD START 13 XMIT Valid Valid 13 Valid END 13 9

Figure 5-24. MMC/SD Host Command Timing

7 MMCSD_CLK 1 2 MMCSD_CMD START XMIT Valid Valid Valid END 9 10

Figure 5-25. MMC/SD Card Response Timing

10 7 MMCSD_CLK 14 MMCSD_DATx START 14 D0 D1 14 Dx END 14 9

Figure 5-26. MMC/SD Host Write Timing

9 7 MMCSD_CLK 4 3 MMCSD_DATx Start D0 D1 Dx 3 End 4 10

Figure 5-27. MMC/SD Host Read and Card CRC Status Timing

126

Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): AM1810

Copyright © 2010, Texas Instruments Incorporated

AM1810

www. ti. com SPRS709 NOVEMBER 2010

5. 14 Serial ATA Controller (SATA)

The Serial ATA Controller (SATA) provides a single HBA port operating in AHCI mode and is used to interface to data storage devices at both 1. 5 Gbits/second and 3. 0 Gbits/second line speeds. AHCI describes a system memory structure that contains a generic area for control and status, and a table of entries describing a command list where each command list entry contains information necessary to program an SATA device, and a pointer to a descriptor table for transferring data between system memory and the device. The SATA Controller supports the following features: · · · · · · · · · · · · Serial ATA 1. 5 Gbps (Gen 1i) and 3 Gbps (Gen 2i) line speeds Support for the AHCI controller spec 1. 1 Integrated SERDES PHY Integrated Rx and Tx data buffers Supports all SATA power management features Internal DMA engine per port Hardware-assisted native command queuing (NCQ) for up to 32 entries 32-bit addressing Supports port multiplier with command-based switching Activity LED support Mechanical presence switch Cold presence detect

The SATA Controller support is dependent on the CPU voltage operating point: · · · At CVDD = 1. 2V, SATA Gen 2i (3. 0 Gbps) and SATA Gen 1i (1. 5 Gbps) are supported. At CVDD = 1. 1V, SATA Gen 1i (1. 5 Gbps) only is supported. At CVDD = 1. 0V, SATA is not supported.

Copyright © 2010, Texas Instruments Incorporated

Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): AM1810

127

AM1810

SPRS709 NOVEMBER 2010 www. ti. com

5. 14. 1 SATA Register Descriptions

Table 5-42 is a list of the SATA Controller registers. SATA Controller Registers

BYTE ADDRESS 0x01E1 8000 0x01E1 8004 0x01E1 8008 0x01E1 800C 0x01E1 8010 0x01E1 8014 0x01E1 8018 0x01E1 80A0 0x01E1 80A4 0x01E1 80A8 0x01E1 80AC 0x01E1 80B0 0x01E1 80E0 0x01E1 80E8 0x01E1 80EC 0x01E1 80F0 0x01E1 80F4 0x01E1 80F8 0x01E1 80FC 0x01E1 8100 0x01E1 8108 0x01E1 8110 0x01E1 8114 0x01E1 8118 0x01E1 8120 0x01E1 8124 0x01E1 8128 0x01E1 812C 0x01E1 8130 0x01E1 8134 0x01E1 8138 0x01E1 813C 0x01E1 8170 0x01E1 8178 0x01E1 817C ACRONYM CAP GHC IS PI VS CCC_CTL CCC_PORTS BISTAFR BISTCR BISTFCTR BISTSR BISTDECR TIMER1MS GPARAM1R GPARAM2R PPARAMR TESTR VERSIONR IDR P0CLB P0FB P0IS P0IE P0CMD P0TFD P0SIG P0SSTS P0SCTL P0SERR P0SACT P0CI P0SNTF P0DMACR P0PHYCR P0PHYSR HBA Capabilities Register Global HBA Control Register Interrupt Status Register Ports Implemented Register AHCI Version Register Command Completion Coalescing Control Register Command Completion Coalescing Ports Register BIST Active FIS Register BIST Control Register BIST FIS Count Register BIST Status Register BIST DWORD Error Count Register BIST DWORD Error Count Register Global Parameter 1 Register Global Parameter 2 Register Port Parameter Register Test Register Version Register ID Register Port Command List Base Address Register Port FIS Base Address Register Port Interrupt Status Register Port Interrupt Enable Register Port Command Register Port Task File Data Register Port Signature Register Port Serial ATA Status Register Port Serial ATA Control Register Port Serial ATA Error Register Port Serial ATA Active Register Port Command Issue Register Port Serial ATA Notification Register Port DMA Control Register Port PHY Control Register Port PHY Status Register REGISTER DESCRIPTION

128

Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): AM1810

Copyright © 2010, Texas Instruments Incorporated

AM1810

www. ti. com SPRS709 NOVEMBER 2010

5. 14. 2 1. SATA Interface

This section provides the timing specification for the SATA interface as a PCB design and manufacturing specification. The design rules constrain PCB trace length, PCB trace skew, signal integrity, cross-talk, and signal timing. TI has performed the simulation and system design work to ensure the SATA interface requirements are met. 5. 14. 2. 1 SATA Interface Schematic Figure 5-28 shows the SATA interface schematic.

SATA Interface(Processor) SATA_TXN SATA_TXP SATA_RXN SATA_RXP 10nF 10nF 10nF 10nF SATA Connector TX TX+ RX RX+ LVDS Oscillator CLK CLK+

10nF SATA_REFCLKN SATA_REFCLKP 10nF

SATA_REG

0. 1uF

Figure 5-28. SATA Interface High Level Schematic 5. 14. 2. 2 Compatible SATA Components and Modes Table 5-43 shows the compatible SATA components and supported modes. Note that the only supported configuration is an internal cable from the processor host to the SATA device. SATA Supported Modes

PARAMETER Transfer Rates eSATA xSATA Backplane Internal Cable MIN 1. 5 MAX 3. 0 UNIT Gbps No No No Yes SUPPORTED

5. 14. 2. 3 PCB Stackup Specifications Table 5-44 shows the stackup and feature sizes required for SATA. [. . . ] All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. [. . . ]

DISCLAIMER TO DOWNLOAD THE USER GUIDE TEXAS INSTRUMENTS AM1810 ARM MICROPROCESSOR Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets...manual TEXAS INSTRUMENTS AM1810 ARM MICROPROCESSOR