User manual TEXAS INSTRUMENTS AM3517 DATA MANUAL REV B

Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets... DON'T FORGET : ALWAYS READ THE USER GUIDE BEFORE BUYING !!!

If this document matches the user guide, instructions manual or user manual, feature sets, schematics you are looking for, download it now. Lastmanuals provides you a fast and easy access to the user manual TEXAS INSTRUMENTS AM3517. We hope that this TEXAS INSTRUMENTS AM3517 user guide will be useful to you.

Lastmanuals help download the user guide TEXAS INSTRUMENTS AM3517.

Manual abstract: user guide TEXAS INSTRUMENTS AM3517DATA MANUAL REV B

Detailed instructions for use are in the User's Guide.

[. . . ] AM3517, AM3505

www. ti. com SPRS550B OCTOBER 2009 REVISED JULY 2010

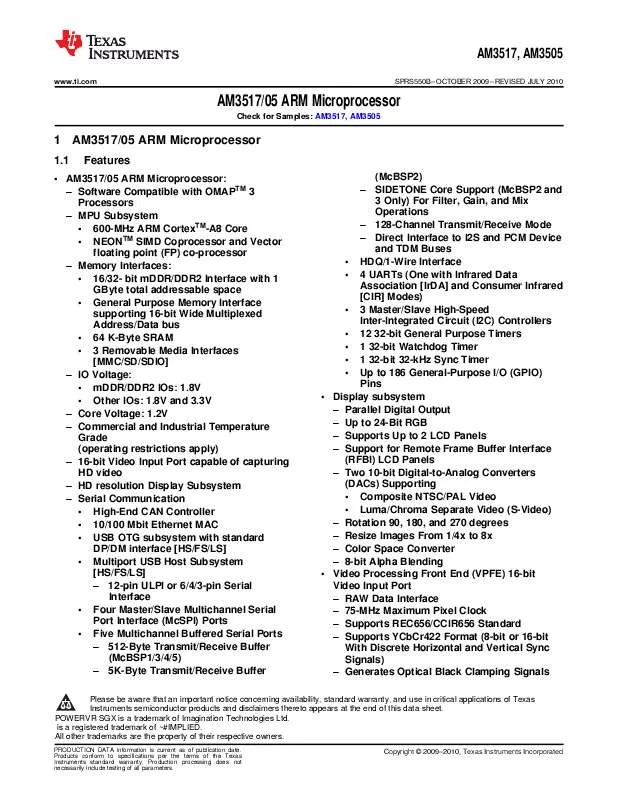

AM3517/05 ARM Microprocessor

Check for Samples: AM3517, AM3505

1 AM3517/05 ARM Microprocessor

1. 1

1234

Features

(McBSP2) SIDETONE Core Support (McBSP2 and 3 Only) For Filter, Gain, and Mix Operations 128-Channel Transmit/Receive Mode Direct Interface to I2S and PCM Device and TDM Buses · HDQ/1-Wire Interface · 4 UARTs (One with Infrared Data Association [IrDA] and Consumer Infrared [CIR] Modes) · 3 Master/Slave High-Speed Inter-Integrated Circuit (I2C) Controllers · 12 32-bit General Purpose Timers · 1 32-bit Watchdog Timer · 1 32-bit 32-kHz Sync Timer · Up to 186 General-Purpose I/O (GPIO) Pins · Display subsystem Parallel Digital Output Up to 24-Bit RGB Supports Up to 2 LCD Panels Support for Remote Frame Buffer Interface (RFBI) LCD Panels Two 10-bit Digital-to-Analog Converters (DACs) Supporting · Composite NTSC/PAL Video · Luma/Chroma Separate Video (S-Video) Rotation 90, 180, and 270 degrees Resize Images From 1/4x to 8x Color Space Converter 8-bit Alpha Blending · Video Processing Front End (VPFE) 16-bit Video Input Port RAW Data Interface 75-MHz Maximum Pixel Clock Supports REC656/CCIR656 Standard Supports YCbCr422 Format (8-bit or 16-bit With Discrete Horizontal and Vertical Sync Signals) Generates Optical Black Clamping Signals

· AM3517/05 ARM Microprocessor: Software Compatible with OMAPTM 3 Processors MPU Subsystem · 600-MHz ARM CortexTM-A8 Core · NEONTM SIMD Coprocessor and Vector floating point (FP) co-processor Memory Interfaces: · 16/32- bit mDDR/DDR2 Interface with 1 GByte total addressable space · General Purpose Memory Interface supporting 16-bit Wide Multiplexed Address/Data bus · 64 K-Byte SRAM · 3 Removable Media Interfaces [MMC/SD/SDIO] IO Voltage: · mDDR/DDR2 IOs: 1. 8V · Other IOs: 1. 8V and 3. 3V Core Voltage: 1. 2V Commercial and Industrial Temperature Grade (operating restrictions apply) 16-bit Video Input Port capable of capturing HD video HD resolution Display Subsystem Serial Communication · High-End CAN Controller · 10/100 Mbit Ethernet MAC · USB OTG subsystem with standard DP/DM interface [HS/FS/LS] · Multiport USB Host Subsystem [HS/FS/LS] 12-pin ULPI or 6/4/3-pin Serial Interface · Four Master/Slave Multichannel Serial Port Interface (McSPI) Ports · Five Multichannel Buffered Serial Ports 512-Byte Transmit/Receive Buffer (McBSP1/3/4/5) 5K-Byte Transmit/Receive Buffer

1

2

3

4

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. POWERVR SGX is a trademark of Imagination Technologies Ltd. All other trademarks are the property of their respective owners.

Copyright © 20092010, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. [. . . ] The route is a balanced T as it is intended that the length of segments B and C be equal. In addition, the length of A should be maximized.

A1

B

T A C

LPDDR Controller

AM35x

A1

Figure 6-21. CK and ADDR_CTRL Routing and Topology Table 6-20. CK and ADDR_CTRL Routing Specification

NO. 1 2 3 4 5 6 7 8 9 10 11 (1) (2) (3) PARAMETER Center to Center CK-CK spacing CK A to B/A to C Skew Length Mismatch CK B to C Skew Length Mismatch Center to Center CK to other LPDDR trace spacing CK/ADDR_CTRL nominal trace length ADDR_CTRL to CK Skew Length Mismatch ADDR_CTRL to ADDR_CTRL Skew Length Mismatch Center to Center ADDR_CTRL to other LPDDR trace 4w spacing Center to Center ADDR_CTRL to other ADDR_CTRL 3w trace spacing ADDR_CTRL A to B/A to C Skew Length Mismatch ADDR_CTRL B to C Skew Length Mismatch 4w 3w 100 100 Mils Mils 4w CACLM-50 CACLM CACLM+50 100 100 Mils Mils Mils See Note (2) See Note (2) See Note (1) MIN TYP MAX 2w 25 25 Mils Mils See Note (2) See Note (3) See Note (1) UNIT NOTES

Series terminator, if used, should be located closest to device. Center to center spacing is allowed to fall to minimum (w) for up to 500 mils of routed length to accommodate BGA escape and routing congestion. CACLM is the longest Manhattan distance of the CK and ADDR_CTRL net classes.

Copyright © 20092010, Texas Instruments Incorporated

TIMING REQUIREMENTS AND SWITCHING CHARACTERISTICS Submit Documentation Feedback Product Folder Link(s): AM3517 AM3505

135

AM3517, AM3505

SPRS550B OCTOBER 2009 REVISED JULY 2010 www. ti. com

Figure 6-22 shows the topology and routing for the DQS and DQ net classes; the routes are point to point. Skew matching across bytes is not needed nor recommended.

T A1 T E0 E1

LPDDR Controller

T A1 E2 T E3 AM35x

Figure 6-22. DQS and DQ Routing and Topology Table 6-21. DQS and DQ Routing Specification (1)

NO. 2 3 4 5 6 7 8 9 (1) (2) (3) (4) PARAMETER DQS E Skew Length Mismatch Center to Center DQS to other LPDDR trace spacing DQS/DQ nominal trace length DQ to DQS Skew Length Mismatch DQ to DQ Skew Length Mismatch Center to Center DQ to other LPDDR trace spacing Center to Center DQ to other DQ trace spacing DQ E Skew Length Mismatch 4w 3w 100 Mils 4w DQLM - 50 DQLM DQLM + 50 100 100 Mils Mils Mils See Note (2) See Note (2), (4) MIN TYP MAX 25 UNIT Mils See Note (2) See Note (3) NOTES

Series terminator, if used, should be located closest to LPDDR. Center to center spacing is allowed to fall to minimum (w) for up to 500 mils of routed length to accommodate BGA escape and routing congestion. Center to center spacing is allowed to fall to minimum (w) for up to 500 mils of routed length to accommodate BGA escape and routing congestion. DQLM is the longest Manhattan distance of the DQS and DQ net classes.

136

TIMING REQUIREMENTS AND SWITCHING CHARACTERISTICS Copyright © 20092010, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Link(s): AM3517 AM3505

AM3517, AM3505

www. ti. com SPRS550B OCTOBER 2009 REVISED JULY 2010

6. 4. 2. 2

DDR2 Interface

This section provides the timing specification for the DDR2 interface as a PCB design and manufacturing specification. The design rules constrain PCB trace length, PCB trace skew, signal integrity, cross-talk, and signal timing. These rules, when followed, result in a reliable DDR2 memory system without the need for a complex timing closure process. For more information regarding guidelines for using this DDR2 specification, Understanding TI's PCB Routing Rule-Based DDR2 Timing Specification (SPRAAV0). 6. 4. 2. 2. 1 DDR2 Interface Schematic Figure 6-23 shows the DDR2 interface schematic for a dual-memory DDR2 system. The single-memory system is shown in Figure 6-24. Pin numbers for the AM3517/05 can be obtained from the pin description section. 6. 4. 2. 2. 2 Compatible JEDEC DDR2 Devices Table 6-22 shows the parameters of the JEDEC DDR2 devices that are compatible with this interface. Generally, the DDR2 interface is compatible with x16 or x32 DDR2 speed grade DDR2-333 devices. [. . . ] All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. [. . . ]

DISCLAIMER TO DOWNLOAD THE USER GUIDE TEXAS INSTRUMENTS AM3517 Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets...manual TEXAS INSTRUMENTS AM3517