User manual TEXAS INSTRUMENTS AM3703 DATA MANUAL REV B

Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets... DON'T FORGET : ALWAYS READ THE USER GUIDE BEFORE BUYING !!!

If this document matches the user guide, instructions manual or user manual, feature sets, schematics you are looking for, download it now. Lastmanuals provides you a fast and easy access to the user manual TEXAS INSTRUMENTS AM3703. We hope that this TEXAS INSTRUMENTS AM3703 user guide will be useful to you.

Lastmanuals help download the user guide TEXAS INSTRUMENTS AM3703.

You may also download the following manuals related to this product:

Manual abstract: user guide TEXAS INSTRUMENTS AM3703DATA MANUAL REV B

Detailed instructions for use are in the User's Guide.

[. . . ] AM3715/03

www. ti. com SPRS616B JUNE 2010 REVISED JULY 2010

AM3715/03 Applications Processor

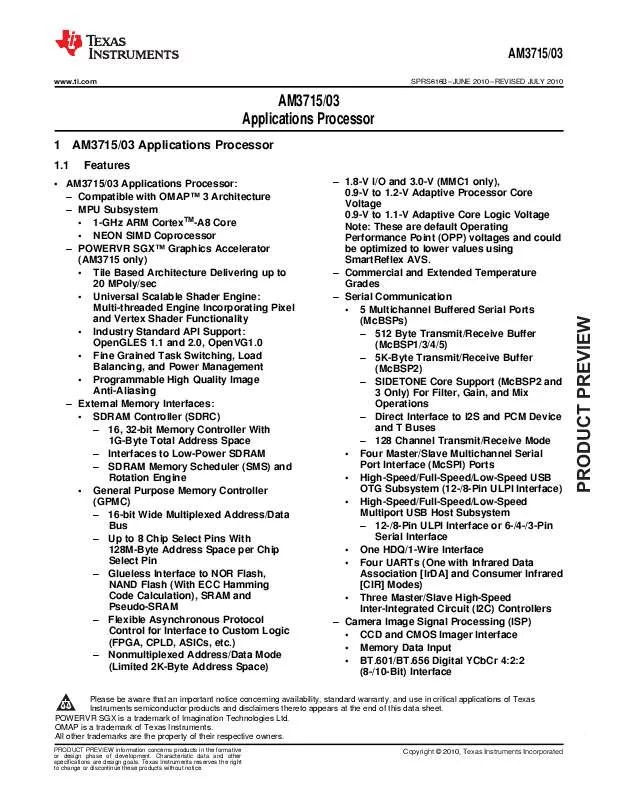

1 AM3715/03 Applications Processor

1. 1

1234

Features

1. 8-V I/O and 3. 0-V (MMC1 only), 0. 9-V to 1. 2-V Adaptive Processor Core Voltage 0. 9-V to 1. 1-V Adaptive Core Logic Voltage Note: These are default Operating Performance Point (OPP) voltages and could be optimized to lower values using SmartReflex AVS. Commercial and Extended Temperature Grades Serial Communication · 5 Multichannel Buffered Serial Ports (McBSPs) 512 Byte Transmit/Receive Buffer (McBSP1/3/4/5) 5K-Byte Transmit/Receive Buffer (McBSP2) SIDETONE Core Support (McBSP2 and 3 Only) For Filter, Gain, and Mix Operations Direct Interface to I2S and PCM Device and T Buses 128 Channel Transmit/Receive Mode · Four Master/Slave Multichannel Serial Port Interface (McSPI) Ports · High-Speed/Full-Speed/Low-Speed USB OTG Subsystem (12-/8-Pin ULPI Interface) · High-Speed/Full-Speed/Low-Speed Multiport USB Host Subsystem 12-/8-Pin ULPI Interface or 6-/4-/3-Pin Serial Interface · One HDQ/1-Wire Interface · Four UARTs (One with Infrared Data Association [IrDA] and Consumer Infrared [CIR] Modes) · Three Master/Slave High-Speed Inter-Integrated Circuit (I2C) Controllers Camera Image Signal Processing (ISP) · CCD and CMOS Imager Interface · Memory Data Input · BT. 601/BT. 656 Digital YCbCr 4:2:2 (8-/10-Bit) Interface

· AM3715/03 Applications Processor: Compatible with OMAPTM 3 Architecture MPU Subsystem · 1-GHz ARM CortexTM-A8 Core · NEON SIMD Coprocessor POWERVR SGXTM Graphics Accelerator (AM3715 only) · Tile Based Architecture Delivering up to 20 MPoly/sec · Universal Scalable Shader Engine: Multi-threaded Engine Incorporating Pixel and Vertex Shader Functionality · Industry Standard API Support: OpenGLES 1. 1 and 2. 0, OpenVG1. 0 · Fine Grained Task Switching, Load Balancing, and Power Management · Programmable High Quality Image Anti-Aliasing External Memory Interfaces: · SDRAM Controller (SDRC) 16, 32-bit Memory Controller With 1G-Byte Total Address Space Interfaces to Low-Power SDRAM SDRAM Memory Scheduler (SMS) and Rotation Engine · General Purpose Memory Controller (GPMC) 16-bit Wide Multiplexed Address/Data Bus Up to 8 Chip Select Pins With 128M-Byte Address Space per Chip Select Pin Glueless Interface to NOR Flash, NAND Flash (With ECC Hamming Code Calculation), SRAM and Pseudo-SRAM Flexible Asynchronous Protocol Control for Interface to Custom Logic (FPGA, CPLD, ASICs, etc. ) Nonmultiplexed Address/Data Mode (Limited 2K-Byte Address Space)

1

2

3

4

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. POWERVR SGX is a trademark of Imagination Technologies Ltd. OMAP is a trademark of Texas Instruments. [. . . ] Please see the LPDDR device manufacturer documentation for the LPDDR device BGA pad size. Z is the nominal singled ended impedance selected for the PCB specified by item 12.

170

Timing Requirements and Switching Characteristics Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated

AM3715/03

www. ti. com SPRS616B JUNE 2010 REVISED JULY 2010

5. 5 5. 5. 1

Multimedia Interfaces Camera ISP2P Interface

NOTE

For more information, see Camera ISP chapter of the AM3715/03 TRM.

The camera subsystem provides the system interfaces and the processing capability to connect raw, YUV or JPEG image sensor modules to the AM3715/03 device for video-preview, video-record and still-image-capture applications. The camera ISP2P subsystem supports up to two simultaneous pixel flows but only one of them can use the video processing hardware: · Parallel camera interface + Serial camera interface: one interface data goes through the video processing hardware. The other interface data goes directly to memory · Serial camera interface + Serial camera interface: one serial interface data goes through the video processing hardware. The other serial interface data goes directly to memory. The camera ISP2P subsystem supports different camera configurations: · 10-bit Parallel interface · 12-bit Parallel interface · 12-bit Parallel interface Note: For more information, see the Camera ISP / Camera ISP Environment / Camera ISP Connectivity Schemes section of the AM3715/03 TRM. 5. 5. 1. 1 Camera Output Clocks (cam_xclka and cam_xclkb) Table 5-16. ISP2P cam_xclka and cam_xclkb Output Clocks Switching Characteristics

NO. ISP15 ISP16 ISP16 1 / tc(xclk) tw(xclkH) tw(xclkL) tdc(xclk) tJ(xclk) tR(xclk) tF(xclk) PARAMETER Frequency(1), output clock cam_xclkn(4) Typical pulse duration, output clock cam_xclkn Duty cycle error, output clock cam_xclkn(4) Jitter standard deviation , output clock cam_xclkn Rise time, output clock cam_xclkn(4) Fall time, output clock cam_xclkn(4)

(4) (3) (4) (4)

OPP100 MIN high 0. 5P MAX 216

(2)

OPP50 MIN 0. 5P MAX 216

(2)

UNIT MHz ns ns 231 33 ps ps ns ns

Typical pulse duration, output clock cam_xclkn(4) low

0. 5P(2) 231 33 0. 93 0. 93

0. 5P(2)

0. 93 0. 93

(1) Related with the cam_xclkn maximum and minimum frequencies programmable in the ISP module. NOTE: You must disable the camera sensor or the camera module to change the frequency configuration. For more information, see the AM3715/03 TRM. (2) P = cam_xclkn(4) period in ns (3) The jitter probability density can be approximated by a Gaussian function. (4) In cam_xclkn, n is equal to a or b.

5. 5. 1. 2

Parallel Camera Interface (CPI)

5. 5. 1. 2. 1 CPI--Video and Graphics Digitizer 1. 8V Mode The imaging subsystem deals with the processing of the pixel data coming from an external image sensor or from video and graphics digitizer. It is a key component for the following multimedia applications: video preview, camera viewfinder, video record and still image capture. It supports RAW, RGB, and YUV data processing.

Copyright © 2010, Texas Instruments Incorporated

Timing Requirements and Switching Characteristics Submit Documentation Feedback

171

PRODUCT PREVIEW

AM3715/03

SPRS616B JUNE 2010 REVISED JULY 2010 www. ti. com

Table 5-18 assumes testing over the recommended operating conditions and electrical characteristic conditions below (see Figure 5-19 and Figure 5-20). CPI Timing Conditions--Video and Graphics Digitizer 1. 8-V Mode

TIMING CONDITION PARAMETER MIN Input Conditions tR tF Input signal rise time Input signal fall time 80 80 1800 1800 ps ps VALUE MAX UNIT

Table 5-18. CPI Timing Requirements--Video and Graphics Digitizer 1. 8-V Mode(4) (6)

NO. ISP1 ISP2 ISP3 1 / tc(pclk) tw(pclkL) tw(pclkH) tdc(pclk) PARAMETER Frequency(1), input pixel clock cam_pclk Typical pulse duration, input pixel clock cam_pclk low Typical pulse duration, input pixel clock cam_pclk high Duty cycle error, input pixel clock cam_pclk Cycle jitter(3), input pixel clock cam_pclk Setup time, input vertical synchronization cam_vs valid before input pixel clock cam_pclk rising/falling edge Hold time, input vertical synchronization cam_vs valid after input pixel clock cam_pclk rising/falling edge Setup time, input horizontal synchronization cam_hs valid before input pixel clock cam_pclk rising/falling edge Hold time, input horizontal synchronization cam_hs valid after input pixel clock cam_pclk rising/falling edge Setup time, input data cam_d[n:0](5) valid before input pixel clock cam_pclk rising/falling edge Hold time, input data cam_d[n:0](5) valid after input pixel clock cam_pclk rising/falling edge Setup time, input write enable cam_wen valid before input pixel clock cam_pclk rising/falling edge Hold time, input write enable cam_wen valid after input pixel clock cam_pclk rising/falling edge Setup time, input field identification cam_fld valid before input pixel clock cam_pclk rising/falling edge Hold time, input field identification cam_fld valid after input pixel clock cam_pclk rising/falling edge 0. 75 0. 96 0. 75 0. 96 0. 75 0. 96 0. 75 0. 96 0. 75 0. 96 0. 5P

(2)

OPP100 MIN MAX 148. 5 0. 5P(2) 0. 5*P(2) 3. 247 0. 06P(2)

UNIT MHz ns ns ns ns ns ns ns ns ns ns ns ns ns ns

PRODUCT PREVIEW

tJ(pclk) ISP4 ISP5 ISP6 ISP7 ISP8 ISP9 ISP10 ISP11 ISP12 ISP13 tsu(vsV-pclkH) th(pclkH-vsV) tsu(hsV-pclkH) th(pclkH-hsV) tsu(dV-pclkH) th(pclkH-dV) tsu(wenV-pclkH) th(pclkH-wenV) tsu(fldV-pclkH) th(pclkH-fldV)

(1) Related with the input maximum frequency supported by the ISP module in 8-bit mode with 8 to 16 data bits conversion bridge enabled. (2) P = cam_pclk period in ns (3) Maximum cycle jitter supported by cam_pclk input clock (4) The timing requirements are assured up to the cycle jitter and duty cycle error conditions specified. (5) n = 11 (Data bus size is limited to 8 bits. So the bits configuration is either cam_d[7:0] or cam_d[11:4]). (6) See Operating Condition Addendum for OPP voltages.

172

Timing Requirements and Switching Characteristics Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated

AM3715/03

www. ti. com SPRS616B JUNE 2010 REVISED JULY 2010

ISP3 ISP1 cam_pclk ISP2

ISP4 cam_vs

ISP5

ISP6 cam_hs

ISP7

ISP8 ISP9 cam_d[N:0]

D(0) D(n-2) D(n-1) D(0) D(n-2) D(n-1)

ISP10 cam_wen

ISP11

cam_fld

SWPS038-048

(1) (2)

The polarity of cam_pclk, cam_fld, cam_vs, and cam_hs are software configurable. [. . . ] All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. [. . . ]

DISCLAIMER TO DOWNLOAD THE USER GUIDE TEXAS INSTRUMENTS AM3703 Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets...manual TEXAS INSTRUMENTS AM3703

TEXAS INSTRUMENTS AM3703 PRODUCT PREVIEW (2995 ko)

TEXAS INSTRUMENTS AM3703 PRODUCT PREVIEW (2995 ko)

TEXAS INSTRUMENTS AM3703 FEATURES 10-2010 (2592 ko)

TEXAS INSTRUMENTS AM3703 FEATURES 10-2010 (2592 ko)

TEXAS INSTRUMENTS AM3703 PRODUCT PREVIEW 08-2010 (2995 ko)

TEXAS INSTRUMENTS AM3703 PRODUCT PREVIEW 08-2010 (2995 ko)