User manual TEXAS INSTRUMENTS DM3725 PRODUCT PREVIEW 08-2010

Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets... DON'T FORGET : ALWAYS READ THE USER GUIDE BEFORE BUYING !!!

If this document matches the user guide, instructions manual or user manual, feature sets, schematics you are looking for, download it now. Lastmanuals provides you a fast and easy access to the user manual TEXAS INSTRUMENTS DM3725. We hope that this TEXAS INSTRUMENTS DM3725 user guide will be useful to you.

Lastmanuals help download the user guide TEXAS INSTRUMENTS DM3725.

You may also download the following manuals related to this product:

Manual abstract: user guide TEXAS INSTRUMENTS DM3725PRODUCT PREVIEW 08-2010

Detailed instructions for use are in the User's Guide.

[. . . ] DM3730, DM3725

www. ti. com SPRS685A AUGUST 2010 REVISED SEPTEMBER 2010

DM3730, DM3725 Digital Media Processor

Check for Samples: DM3730, DM3725

1 DM3730, DM3725 Digital Media Processor

1. 1

12345

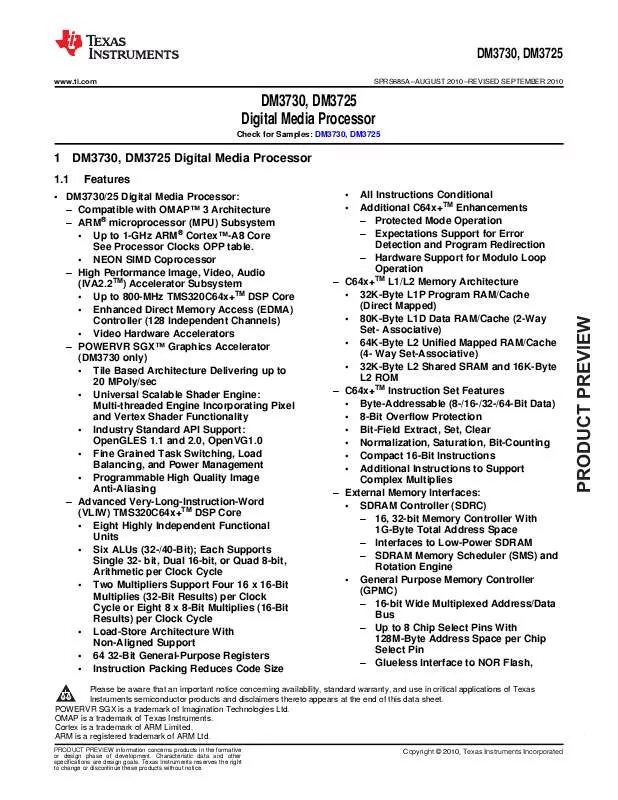

Features

All Instructions Conditional Additional C64x+TM Enhancements Protected Mode Operation Expectations Support for Error Detection and Program Redirection Hardware Support for Modulo Loop Operation C64x+TM L1/L2 Memory Architecture · 32K-Byte L1P Program RAM/Cache (Direct Mapped) · 80K-Byte L1D Data RAM/Cache (2-Way Set- Associative) · 64K-Byte L2 Unified Mapped RAM/Cache (4- Way Set-Associative) · 32K-Byte L2 Shared SRAM and 16K-Byte L2 ROM C64x+TM Instruction Set Features · Byte-Addressable (8-/16-/32-/64-Bit Data) · 8-Bit Overflow Protection · Bit-Field Extract, Set, Clear · Normalization, Saturation, Bit-Counting · Compact 16-Bit Instructions · Additional Instructions to Support Complex Multiplies External Memory Interfaces: · SDRAM Controller (SDRC) 16, 32-bit Memory Controller With 1G-Byte Total Address Space Interfaces to Low-Power SDRAM SDRAM Memory Scheduler (SMS) and Rotation Engine · General Purpose Memory Controller (GPMC) 16-bit Wide Multiplexed Address/Data Bus Up to 8 Chip Select Pins With 128M-Byte Address Space per Chip Select Pin Glueless Interface to NOR Flash, · ·

· DM3730/25 Digital Media Processor: Compatible with OMAPTM 3 Architecture ARM® microprocessor (MPU) Subsystem · Up to 1-GHz ARM® CortexTM-A8 Core See Processor Clocks OPP table. · NEON SIMD Coprocessor High Performance Image, Video, Audio (IVA2. 2TM) Accelerator Subsystem · Up to 800-MHz TMS320C64x+TM DSP Core · Enhanced Direct Memory Access (EDMA) Controller (128 Independent Channels) · Video Hardware Accelerators POWERVR SGXTM Graphics Accelerator (DM3730 only) · Tile Based Architecture Delivering up to 20 MPoly/sec · Universal Scalable Shader Engine: Multi-threaded Engine Incorporating Pixel and Vertex Shader Functionality · Industry Standard API Support: OpenGLES 1. 1 and 2. 0, OpenVG1. 0 · Fine Grained Task Switching, Load Balancing, and Power Management · Programmable High Quality Image Anti-Aliasing Advanced Very-Long-Instruction-Word (VLIW) TMS320C64x+TM DSP Core · Eight Highly Independent Functional Units · Six ALUs (32-/40-Bit); Each Supports Single 32- bit, Dual 16-bit, or Quad 8-bit, Arithmetic per Clock Cycle · Two Multipliers Support Four 16 x 16-Bit Multiplies (32-Bit Results) per Clock Cycle or Eight 8 x 8-Bit Multiplies (16-Bit Results) per Clock Cycle · Load-Store Architecture With Non-Aligned Support · 64 32-Bit General-Purpose Registers · Instruction Packing Reduces Code Size

1

2

3

4

5

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. POWERVR SGX is a trademark of Imagination Technologies Ltd. OMAP is a trademark of Texas Instruments. [. . . ] The size of this region varies with the placement and LPDDR routing. Additional clearances required for the keep out region are shown in Table 5-16.

Copyright © 2010, Texas Instruments Incorporated

Timing Requirements and Switching Characteristics Submit Documentation Feedback Product Folder Link(s): DM3730 DM3725

175

PRODUCT PREVIEW

DM3730, DM3725

SPRS685A AUGUST 2010 REVISED SEPTEMBER 2010 www. ti. com

A1

LPDDR Controller

LPDDR Device

A1

Region should encompass all LPDDR circuitry and varies depending on placement. Non-LPDDR signals should not be routed on the LPDDR signal layers within the LPDDR keep out region. Non-LPDDR signals may be routed in the region provided they are routed on layers separated from LPDDR signal layers by a ground layer. No breaks should be allowed in the reference ground layers in this region. In addition, the 1. 8 V power plane should cover the entire keep out region.

Figure 5-20. LPDDR Keepout Region

PRODUCT PREVIEW

5. 4. 2. 4

Net Classes

Table 5-17 lists the clock net classes for the LPDDR interface. Table 5-18 lists the signal net classes, and associated clock net classes, for the signals in the LPDDR interface. These net classes are used for the termination and routing rules that follow. Clock Net Class Definitions

CLOCK NET CLASS CK DQS0 DQS1 DQS2 DQS3 PIN NAMES sdrc_clk/sdrc_nclk sdrc_dqs0 sdrc_dqs1 sdrc_dqs2 sdrc_dqs3

Table 5-18. Signal Net Class Definitions

CLOCK NET CLASS ADDR_CTRL DQ0 DQ1 DQ2 DQ3 ASSOCIATED CLOCK NET CLASS CK DQS0 DQS1 DQS2 DQS3 PIN NAMES sdrc_ba[1:0], sdrc_a[14:0], sdrc_ncs[1:0], sdrc_ncas, sdrc_nras, sdrc_nwe, sdrc_cke[1:0] sdrc_d[7:0], sdrc_dm0 sdrc_d[15:8], sdrc_dm1 sdrc_d[23:16], sdrc_dm2 sdrc_d[31:24], sdrc_dm3

5. 4. 2. 5

LPDDR Signal Termination

No terminations of any kind are required in order to meet signal integrity and overshoot requirements. Serial terminators are permitted, if desired, to reduce EMI risk; however, serial terminations are the only type permitted. Table 5-19 shows the specifications for the series terminators.

176

Timing Requirements and Switching Characteristics Submit Documentation Feedback Product Folder Link(s): DM3730 DM3725

Copyright © 2010, Texas Instruments Incorporated

DM3730, DM3725

www. ti. com SPRS685A AUGUST 2010 REVISED SEPTEMBER 2010

Table 5-19. 1 2 3 (1) (2) (3) PARAMETER CK Net Class ADDR_CTRL Net Class Data Byte Net Classes (DQS0-DQS3, DQ0-DQ3) MIN 0 0 0 22 22 TYP MAX 10 Zo Zo UNIT NOTES See Note (1) See Notes (1), (2), (3) See Notes (1), (2), (3)

Only series termination is permitted, parallel or SST specifically disallowed. Terminator values larger than typical only recommended to address EMI issues. Termination value should be uniform across net class.

5. 4. 2. 6

LPDDR CK and ADDR_CTRL Routing

Figure 5-21 shows the topology of the routing for the CK and ADDR_CTRL net classes. The route is a balanced T as it is intended that the length of segments B and C be equal. In addition, the length of A should be maximized.

A1

B

LPDDR Controller

T A C

OMAP A1

Figure 5-21. CK and ADDR_CTRL Routing and Topology Table 5-20. CK and ADDR_CTRL Routing Specification

NO. 1 2 3 4 5 6 7 8 9 10 11 (1) (2) (3) (4) PARAMETER Center to Center CK-CK spacing CK Differential Pair Skew Length Mismatch (1) CK B to C Skew Length Mismatch Center to Center CK to other LPDDR trace spacing CK/ADDR_CTRL nominal trace length ADDR_CTRL to CK Skew Length Mismatch ADDR_CTRL to ADDR_CTRL Skew Length Mismatch Center to Center ADDR_CTRL to other LPDDR trace spacing Center to Center ADDR_CTRL to other ADDR_CTRL trace spacing ADDR_CTRL A to B, ADDR_CTRL A to C Skew Length Mismatch ADDR_CTRL B to C Skew Length Mismatch 4w 3w 100 100 Mils Mils 4w CACLM-50 CACLM CACLM+50 100 100 Mils Mils Mils See Note (3) See Note (3) See Note (2) MIN TYP MAX 2w 25 25 Mils Mils See Note (3) See Note (4) See Note (2) UNIT NOTES

Differential impedance should be 100 ohms Series terminator, if used, should be located closest to DM37x. Center to center spacing is allowed to fall to minimum (w) for up to 500 mils of routed length to accommodate BGA escape and routing congestion. [. . . ] All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. [. . . ]

DISCLAIMER TO DOWNLOAD THE USER GUIDE TEXAS INSTRUMENTS DM3725 Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets...manual TEXAS INSTRUMENTS DM3725

TEXAS INSTRUMENTS DM3725 FEATURES 10-2010 (2600 ko)

TEXAS INSTRUMENTS DM3725 FEATURES 10-2010 (2600 ko)