Detailed instructions for use are in the User's Guide.

[. . . ] OMAP-L137

www. ti. com SPRS563D SEPTEMBER 2008 REVISED AUGUST 2010

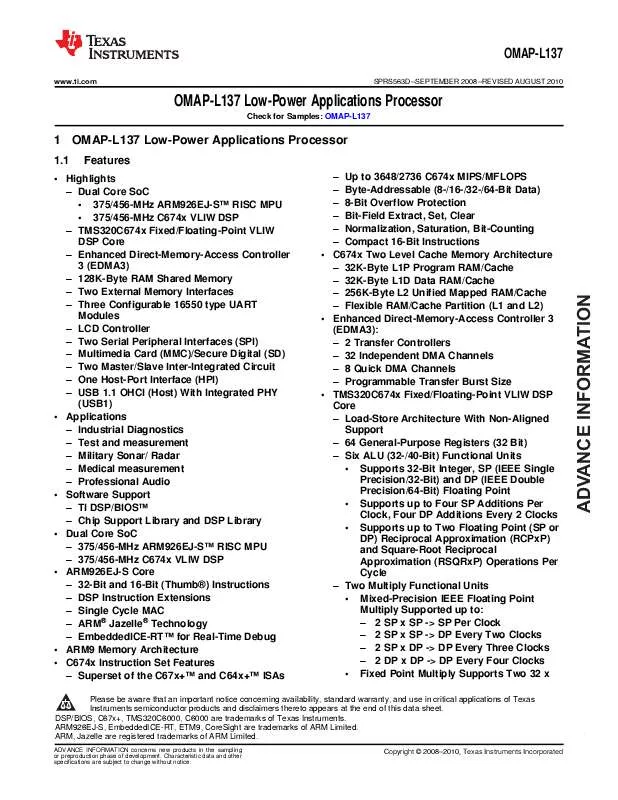

OMAP-L137 Low-Power Applications Processor

Check for Samples: OMAP-L137

1 OMAP-L137 Low-Power Applications Processor

1. 1

1234

Features

Up to 3648/2736 C674x MIPS/MFLOPS Byte-Addressable (8-/16-/32-/64-Bit Data) 8-Bit Overflow Protection Bit-Field Extract, Set, Clear Normalization, Saturation, Bit-Counting Compact 16-Bit Instructions · C674x Two Level Cache Memory Architecture 32K-Byte L1P Program RAM/Cache 32K-Byte L1D Data RAM/Cache 256K-Byte L2 Unified Mapped RAM/Cache Flexible RAM/Cache Partition (L1 and L2) · Enhanced Direct-Memory-Access Controller 3 (EDMA3): 2 Transfer Controllers 32 Independent DMA Channels 8 Quick DMA Channels Programmable Transfer Burst Size · TMS320C674x Fixed/Floating-Point VLIW DSP Core Load-Store Architecture With Non-Aligned Support 64 General-Purpose Registers (32 Bit) Six ALU (32-/40-Bit) Functional Units · Supports 32-Bit Integer, SP (IEEE Single Precision/32-Bit) and DP (IEEE Double Precision/64-Bit) Floating Point · Supports up to Four SP Additions Per Clock, Four DP Additions Every 2 Clocks · Supports up to Two Floating Point (SP or DP) Reciprocal Approximation (RCPxP) and Square-Root Reciprocal Approximation (RSQRxP) Operations Per Cycle Two Multiply Functional Units · Mixed-Precision IEEE Floating Point Multiply Supported up to: 2 SP x SP -> SP Per Clock 2 SP x SP -> DP Every Two Clocks 2 SP x DP -> DP Every Three Clocks 2 DP x DP -> DP Every Four Clocks · Fixed Point Multiply Supports Two 32 x

· Highlights Dual Core SoC · 375/456-MHz ARM926EJ-STM RISC MPU · 375/456-MHz C674x VLIW DSP TMS320C674x Fixed/Floating-Point VLIW DSP Core Enhanced Direct-Memory-Access Controller 3 (EDMA3) 128K-Byte RAM Shared Memory Two External Memory Interfaces Three Configurable 16550 type UART Modules LCD Controller Two Serial Peripheral Interfaces (SPI) Multimedia Card (MMC)/Secure Digital (SD) Two Master/Slave Inter-Integrated Circuit One Host-Port Interface (HPI) USB 1. 1 OHCI (Host) With Integrated PHY (USB1) · Applications Industrial Diagnostics Test and measurement Military Sonar/ Radar Medical measurement Professional Audio · Software Support TI DSP/BIOSTM Chip Support Library and DSP Library · Dual Core SoC 375/456-MHz ARM926EJ-STM RISC MPU 375/456-MHz C674x VLIW DSP · ARM926EJ-S Core 32-Bit and 16-Bit (Thumb®) Instructions DSP Instruction Extensions Single Cycle MAC ARM® Jazelle® Technology EmbeddedICE-RTTM for Real-Time Debug · ARM9 Memory Architecture · C674x Instruction Set Features Superset of the C67x+TM and C64x+TM ISAs

1

2

3

4

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. DSP/BIOS, C67x+, TMS320C6000, C6000 are trademarks of Texas Instruments. ARM926EJ-S, EmbeddedICE-RT, ETM9, CoreSight are trademarks of ARM Limited. ARM, Jazelle are registered trademarks of ARM Limited.

Copyright © 20082010, Texas Instruments Incorporated

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. [. . . ] Additional (1) SPI0 Master Timings, 4-Pin Enable Option (2)

No. PARAMATER Polarity = 0, Phase = 0, to SPI0_CLK rising Delay from slave assertion of SPI0_ENA active to first SPI0_CLK from master. (4) Polarity = 0, Phase = 1, to SPI0_CLK rising Polarity = 1, Phase = 0, to SPI0_CLK falling Polarity = 1, Phase = 1, to SPI0_CLK falling Polarity = 0, Phase = 0, from SPI0_CLK falling Max delay for slave to deassert SPI0_ENA after final SPI0_CLK edge to ensure master does not begin the next transfer. (5) Polarity = 0, Phase = 1, from SPI0_CLK falling Polarity = 1, Phase = 0, from SPI0_CLK rising Polarity = 1, Phase = 1, from SPI0_CLK rising (1) (2) (3) (4) (5) MIN

MAX 3P + 3 0. 5tc(SPC)M + 3P + 3

UNIT

17

td(ENA_SPC)M

ns 3P + 3 0. 5tc(SPC)M + 3P + 3 0. 5tc(SPC)M + P + 5 P+5 ns 0. 5tc(SPC)M + P + 5 P+5

18

td(SPC_ENA)M

These parameters are in addition to the general timings for SPI master modes (Table 6-56). P = SYSCLK2 period Figure shows only Polarity = 0, Phase = 0 as an example. Table gives parameters for all four master clocking modes. In the case where the master SPI is ready with new data before SPI0_ENA assertion. In the case where the master SPI is ready with new data before SPI0_EN A deassertion.

ADVANCE INFORMATION

Table 6-59. Additional (1) SPI0 Master Timings, 4-Pin Chip Select Option (2)

No. PARAMATER Polarity = 0, Phase = 0, to SPI0_CLK rising Delay from SPI0_SCS active to first SPI0_CLK (4) (5) Polarity = 0, Phase = 1, to SPI0_CLK rising Polarity = 1, Phase = 0, to SPI0_CLK falling Polarity = 1, Phase = 1, to SPI0_CLK falling Polarity = 0, Phase = 0, from SPI0_CLK falling Delay from final SPI0_CLK edge to master deasserting SPI0_SCS

(6) (7)

(3)

MIN 2P - 5 0. 5tc(SPC)M + 2P - 5

MAX

UNIT

19

td(SCS_SPC)M

ns 2P - 5 0. 5tc(SPC)M + 2P - 5 0. 5tc(SPC)M + P - 3 P-3 ns 0. 5tc(SPC)M + P - 3 P-3

20

td(SPC_SCS)M

Polarity = 0, Phase = 1, from SPI0_CLK falling Polarity = 1, Phase = 0, from SPI0_CLK rising Polarity = 1, Phase = 1, from SPI0_CLK rising

(1) (2) (3) (4) (5) (6) (7)

These parameters are in addition to the general timings for SPI master modes (Table 6-56). P = SYSCLK2 period Figure shows only Polarity = 0, Phase = 0 as an example. Table gives parameters for all four master clocking modes. In the case where the master SPI is ready with new data before SPI0_SCS assertion. This delay can be increased under software control by the register bit field SPIDELAY. C2TDELAY[4:0]. Except for modes when SPIDAT1. CSHOLD is enabled and there is additional data to transmit. In this case, SPI0_SCS will remain asserted. This delay can be increased under software control by the register bit field SPIDELAY. T2CDELAY[4:0].

132

Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): OMAP-L137

Copyright © 20082010, Texas Instruments Incorporated

OMAP-L137

www. ti. com SPRS563D SEPTEMBER 2008 REVISED AUGUST 2010

Table 6-60. Additional (1) SPI0 Master Timings, 5-Pin Option (2)

No. PARAMATER Polarity = 0, Phase = 0, from SPI0_CLK falling Polarity = 0, Phase = 1, from SPI0_CLK falling Polarity = 1, Phase = 0, from SPI0_CLK rising Polarity = 1, Phase = 1, from SPI0_CLK rising Polarity = 0, Phase = 0, from SPI0_CLK falling Delay from final SPI0_CLK edge to master deasserting SPI0_SCS (5) (6) Polarity = 0, Phase = 1, from SPI0_CLK falling Polarity = 1, Phase = 0, from SPI0_CLK rising Polarity = 1, Phase = 1, from SPI0_CLK rising 21 td(SCSL_ENAL)M Max delay for slave SPI to drive SPI0_ENA valid after master asserts SPI0_SCS to delay the master from beginning the next transfer, Polarity = 0, Phase = 0, to SPI0_CLK rising Delay from SPI0_SCS active to first SPI0_CLK (7) (8) (9) Polarity = 0, Phase = 1, to SPI0_CLK rising Polarity = 1, Phase = 0, to SPI0_CLK falling Polarity = 1, Phase = 1, to SPI0_CLK falling Polarity = 0, Phase = 0, to SPI0_CLK rising Delay from assertion of SPI0_ENA low to first SPI0_CLK edge. (10) Polarity = 0, Phase = 1, to SPI0_CLK rising Polarity = 1, Phase = 0, to SPI0_CLK falling Polarity = 1, Phase = 1, to SPI0_CLK falling (1) (2) (3) (4) (5) 2P -5 0. 5tc(SPC)M + 2P -5 0. 5tc(SPC)M + P - 3 P-3 MIN

(3)

MAX 0. 5tc(SPC)M + P + 5 P+5

UNIT

18

td(SPC_ENA)M

Max delay for slave to deassert SPI0_ENA after final SPI0_CLK edge to ensure master does not begin the next transfer. (4)

ns 0. 5tc(SPC)M + P + 5 P+5

20

td(SPC_SCS)M

ns 0. 5tc(SPC)M + P -3 P-3

22

td(SCS_SPC)M

ns 2P -5 0. 5tc(SPC)M + 2P -5 3P + 3 0. 5tc(SPC)M + 3P + 3 ns 3P + 3 0. 5tc(SPC)M + 3P + 3

23

td(ENA_SPC)M

These parameters are in addition to the general timings for SPI master modes (Table 6-57). P = SYSCLK2 period Figure shows only Polarity = 0, Phase = 0 as an example. [. . . ] All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. [. . . ]