User manual TEXAS INSTRUMENTS TMS320C6454 DATASHEET 09-2010

Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets... DON'T FORGET : ALWAYS READ THE USER GUIDE BEFORE BUYING !!!

If this document matches the user guide, instructions manual or user manual, feature sets, schematics you are looking for, download it now. Lastmanuals provides you a fast and easy access to the user manual TEXAS INSTRUMENTS TMS320C6454. We hope that this TEXAS INSTRUMENTS TMS320C6454 user guide will be useful to you.

Lastmanuals help download the user guide TEXAS INSTRUMENTS TMS320C6454.

Manual abstract: user guide TEXAS INSTRUMENTS TMS320C6454DATASHEET 09-2010

Detailed instructions for use are in the User's Guide.

[. . . ] TMS320C6454

www. ti. com SPRS311F APRIL 2006 REVISED SEPTEMBER 2010

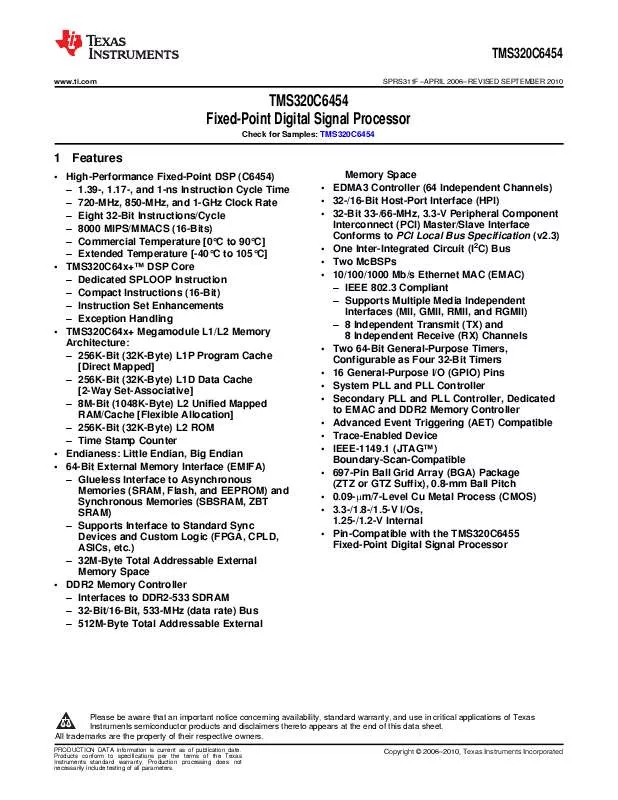

TMS320C6454 Fixed-Point Digital Signal Processor

Check for Samples: TMS320C6454

1 Features

12

· High-Performance Fixed-Point DSP (C6454) 1. 39-, 1. 17-, and 1-ns Instruction Cycle Time 720-MHz, 850-MHz, and 1-GHz Clock Rate Eight 32-Bit Instructions/Cycle 8000 MIPS/MMACS (16-Bits) Commercial Temperature [0°C to 90°C] Extended Temperature [-40°C to 105°C] · TMS320C64x+TM DSP Core Dedicated SPLOOP Instruction Compact Instructions (16-Bit) Instruction Set Enhancements Exception Handling · TMS320C64x+ Megamodule L1/L2 Memory Architecture: 256K-Bit (32K-Byte) L1P Program Cache [Direct Mapped] 256K-Bit (32K-Byte) L1D Data Cache [2-Way Set-Associative] 8M-Bit (1048K-Byte) L2 Unified Mapped RAM/Cache [Flexible Allocation] 256K-Bit (32K-Byte) L2 ROM Time Stamp Counter · Endianess: Little Endian, Big Endian · 64-Bit External Memory Interface (EMIFA) Glueless Interface to Asynchronous Memories (SRAM, Flash, and EEPROM) and Synchronous Memories (SBSRAM, ZBT SRAM) Supports Interface to Standard Sync Devices and Custom Logic (FPGA, CPLD, ASICs, etc. ) 32M-Byte Total Addressable External Memory Space · DDR2 Memory Controller Interfaces to DDR2-533 SDRAM 32-Bit/16-Bit, 533-MHz (data rate) Bus 512M-Byte Total Addressable External

Memory Space · EDMA3 Controller (64 Independent Channels) · 32-/16-Bit Host-Port Interface (HPI) · 32-Bit 33-/66-MHz, 3. 3-V Peripheral Component Interconnect (PCI) Master/Slave Interface Conforms to PCI Local Bus Specification (v2. 3) · One Inter-Integrated Circuit (I2C) Bus · Two McBSPs · 10/100/1000 Mb/s Ethernet MAC (EMAC) IEEE 802. 3 Compliant Supports Multiple Media Independent Interfaces (MII, GMII, RMII, and RGMII) 8 Independent Transmit (TX) and 8 Independent Receive (RX) Channels · Two 64-Bit General-Purpose Timers, Configurable as Four 32-Bit Timers · 16 General-Purpose I/O (GPIO) Pins · System PLL and PLL Controller · Secondary PLL and PLL Controller, Dedicated to EMAC and DDR2 Memory Controller · Advanced Event Triggering (AET) Compatible · Trace-Enabled Device · IEEE-1149. 1 (JTAGTM) Boundary-Scan-Compatible · 697-Pin Ball Grid Array (BGA) Package (ZTZ or GTZ Suffix), 0. 8-mm Ball Pitch · 0. 09-mm/7-Level Cu Metal Process (CMOS) · 3. 3-/1. 8-/1. 5-V I/Os, 1. 25-/1. 2-V Internal · Pin-Compatible with the TMS320C6455 Fixed-Point Digital Signal Processor

1

2

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

Copyright © 20062010, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

TMS320C6454

SPRS311F APRIL 2006 REVISED SEPTEMBER 2010 www. ti. com

1. 1

ZTZ/GTZ BGA Package (Bottom View)

Figure 1-1 shows the TMS320C6454 device 697-pin ball grid array package (bottom view).

ZTZ/GTZ 697-PIN BALL GRID ARRAY (BGA) PACKAGE ( BOTTOM VIEW )

AJ AH AF AD AB Y V U T R P M K J H G F D C B A 1 2 3 4 5 6 7 8 9 11 13 15 17 19 21 23 25 27 29 10 12 14 16 18 20 22 24 26 28 E N L AG AE AC AA W

NOTE: The ZTZ mechanical package designator represents the version of the GTZ package with lead-free balls. [. . . ] Table 7-10 shows the mapping of system events. For more information on the Interrupt Controller, see the TMS320C64x+ Megamodule Reference Guide (literature number SPRU871). C6454 System Event Mapping

EVENT NUMBER 0 (1) 1 (1) 2 (1) 3 (1) 4-8 INTERRUPT EVENT EVT0 EVT1 EVT2 EVT3 Reserved DESCRIPTION Output of event combiner 0 in interrupt controller, for events 1 - 31. Output of event combiner 1 in interrupt controller, for events 32 - 63. Output of event combiner 2 in interrupt controller, for events 64 - 95. Output of event combiner 3 in interrupt controller, for events 96 127. These system events are not connected and, therefore, not used. AET interrupt This system event is not connected and, therefore, not used. EMU real-time data exchange (RTDX) receive complete EMU RTDX transmit complete IDMA channel 0 interrupt IDMA channel 1 interrupt HPI/PCI-to-DSP interrupt I2C interrupt Ethernet MAC interrupt EMIFA error interrupt Reserved. This system event is not connected and, therefore, not used. EDMA3 channel global completion interrupt Reserved. These system events are not connected and, therefore, not used. McBSP0 receive interrupt McBSP0 transmit interrupt McBSP1 receive interrupt McBSP1 transmit interrupt Reserved. These system events are not connected and, therefore, not used. GPIO interrupt GPIO interrupt GPIO interrupt GPIO interrupt GPIO interrupt GPIO interrupt GPIO interrupt

9 (1)

EMU_DTDMA

10 11 (1) 12

(1)

None EMU_RTDXRX EMU_RTDXTX IDMA0 IDMA1 DSPINT I2CINT MACINT AEASYNCERR Reserved EDMA3CC_GINT Reserved RINT0 XINT0 RINT1 XINT1 Reserved GPINT0 GPINT1 GPINT2 GPINT3 GPINT4 GPINT5 GPINT6

13 (1) 14 (1) 15 16 17 18 19 - 23 24 25 - 39 40 41 42 43 44 - 50 51 52 53 54 55 56 57 (1) 116

This system event is generated from within the C64x+ megamodule. C64x+ Peripheral Information and Electrical Specifications Copyright © 20062010, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Link(s): TMS320C6454

TMS320C6454

www. ti. com SPRS311F APRIL 2006 REVISED SEPTEMBER 2010

Table 7-10. C6454 System Event Mapping (continued)

EVENT NUMBER 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 - 95 96 (2) 97

(2)

INTERRUPT EVENT GPINT7 GPINT8 GPINT9 GPINT10 GPINT11 GPINT12 GPINT13 GPINT14 GPINT15 TINTLO0 TINTHI0 TINTLO1 TINTHI1 EDMA3CC_INT0 EDMA3CC_INT1 EDMA3CC_INT2 EDMA3CC_INT3 EDMA3CC_INT4 EDMA3CC_INT5 EDMA3CC_INT6 EDMA3CC_INT7 EDMA3CC_ERRINT Reserved EDMA3TC0_ERRINT EDMA3TC1_ERRINT EDMA3TC2_ERRINT EDMA3TC3_ERRINT Reserved INTERR EMC_IDMAERR Reserved EFIINTA EFIINTB Reserved L1P_ED1 Reserved L2_ED1 L2_ED2 PDC_INT Reserved L1P_CMPA L1P_DMPA GPIO interrupt GPIO interrupt GPIO interrupt GPIO interrupt GPIO interrupt GPIO interrupt GPIO interrupt GPIO interrupt GPIO interrupt

DESCRIPTION

Timer 0 lower counter interrupt Timer 0 higher counter interrupt Timer 1 lower counter interrupt Timer 1 higher counter interrupt EDMA3CC completion interrupt - Mask0 EDMA3CC completion interrupt - Mask1 EDMA3CC completion interrupt - Mask2 EDMA3CC completion interrupt - Mask3 EDMA3CC completion interrupt - Mask4 EDMA3CC completion interrupt - Mask5 EDMA3CC completion interrupt - Mask6 EDMA3CC completion interrupt - Mask7 EDMA3CC error interrupt Reserved. This system event is not connected and, therefore, not used. EDMA3TC0 error interrupt EDMA3TC1 error interrupt EDMA3TC2 error interrupt EDMA3TC3 error interrupt Reserved. These system events are not connected and, therefore, not used. Interrupt Controller dropped CPU interrupt event EMC invalid IDMA parameters Reserved. These system events are not connected and, therefore, not used. [. . . ] All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. [. . . ]

DISCLAIMER TO DOWNLOAD THE USER GUIDE TEXAS INSTRUMENTS TMS320C6454 Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets...manual TEXAS INSTRUMENTS TMS320C6454