Detailed instructions for use are in the User's Guide.

[. . . ] TMS320C6472

www. ti. com SPRS612D JUNE 2009 REVISED JULY 2010

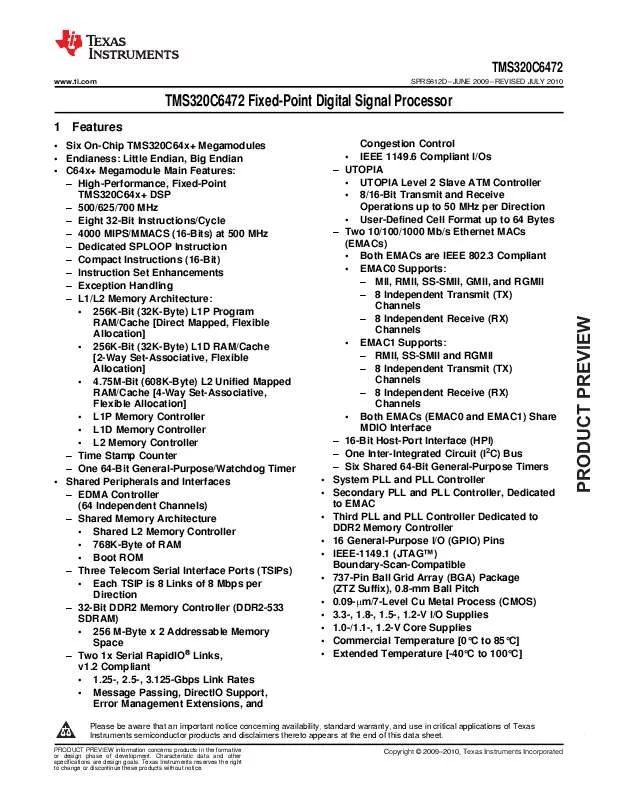

TMS320C6472 Fixed-Point Digital Signal Processor

1 Features

1

· Six On-Chip TMS320C64x+ Megamodules · Endianess: Little Endian, Big Endian · C64x+ Megamodule Main Features: High-Performance, Fixed-Point TMS320C64x+ DSP 500/625/700 MHz Eight 32-Bit Instructions/Cycle 4000 MIPS/MMACS (16-Bits) at 500 MHz Dedicated SPLOOP Instruction Compact Instructions (16-Bit) Instruction Set Enhancements Exception Handling L1/L2 Memory Architecture: · 256K-Bit (32K-Byte) L1P Program RAM/Cache [Direct Mapped, Flexible Allocation] · 256K-Bit (32K-Byte) L1D RAM/Cache [2-Way Set-Associative, Flexible Allocation] · 4. 75M-Bit (608K-Byte) L2 Unified Mapped RAM/Cache [4-Way Set-Associative, Flexible Allocation] · L1P Memory Controller · L1D Memory Controller · L2 Memory Controller Time Stamp Counter One 64-Bit General-Purpose/Watchdog Timer · Shared Peripherals and Interfaces EDMA Controller (64 Independent Channels) Shared Memory Architecture · Shared L2 Memory Controller · 768K-Byte of RAM · Boot ROM Three Telecom Serial Interface Ports (TSIPs) · Each TSIP is 8 Links of 8 Mbps per Direction 32-Bit DDR2 Memory Controller (DDR2-533 SDRAM) · 256 M-Byte x 2 Addressable Memory Space Two 1x Serial RapidIO® Links, v1. 2 Compliant · 1. 25-, 2. 5-, 3. 125-Gbps Link Rates · Message Passing, DirectIO Support, Error Management Extensions, and

1

· · · · · · · · · · ·

Congestion Control · IEEE 1149. 6 Compliant I/Os UTOPIA · UTOPIA Level 2 Slave ATM Controller · 8/16-Bit Transmit and Receive Operations up to 50 MHz per Direction · User-Defined Cell Format up to 64 Bytes Two 10/100/1000 Mb/s Ethernet MACs (EMACs) · Both EMACs are IEEE 802. 3 Compliant · EMAC0 Supports: MII, RMII, SS-SMII, GMII, and RGMII 8 Independent Transmit (TX) Channels 8 Independent Receive (RX) Channels · EMAC1 Supports: RMII, SS-SMII and RGMII 8 Independent Transmit (TX) Channels 8 Independent Receive (RX) Channels · Both EMACs (EMAC0 and EMAC1) Share MDIO Interface 16-Bit Host-Port Interface (HPI) One Inter-Integrated Circuit (I2C) Bus Six Shared 64-Bit General-Purpose Timers System PLL and PLL Controller Secondary PLL and PLL Controller, Dedicated to EMAC Third PLL and PLL Controller Dedicated to DDR2 Memory Controller 16 General-Purpose I/O (GPIO) Pins IEEE-1149. 1 (JTAGTM) Boundary-Scan-Compatible 737-Pin Ball Grid Array (BGA) Package (ZTZ Suffix), 0. 8-mm Ball Pitch 0. 09-mm/7-Level Cu Metal Process (CMOS) 3. 3-, 1. 8-, 1. 5-, 1. 2-V I/O Supplies 1. 0-/1. 1-, 1. 2-V Core Supplies Commercial Temperature [0°C to 85°C] Extended Temperature [-40°C to 100°C]

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

Copyright © 20092010, Texas Instruments Incorporated

PRODUCT PREVIEW

TMS320C6472

SPRS612D JUNE 2009 REVISED JULY 2010 www. ti. com

1. 1

ZTZ BGA Package (Bottom View)

The TMS320C6472 devices are designed for a package temperature range of 0°C to 85°C (commercial temperature range) or -40°C to 100°C (extended temperature range). NOTE

Extended temperature (A) range is available only on 500-MHz and 625-MHz devices.

AJ AH AF AD

AG AE AC

AB AA Y W V U T R P N M L K J H G F E D C B A

PRODUCT PREVIEW

2 Features

1

3 5 7 9 11 13 15 17 19 21 23 25 27 29 2 4 6 8 10 12 14 16 18 20 22 24 26 28

Figure 1-1. [. . . ] For more CPU CSR related information, see the TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (literature number SPRU732).

110

C64x+ Megamodule Submit Documentation Feedback Product Folder Link(s) :TMS320C6472

Copyright © 20092010, Texas Instruments Incorporated

TMS320C6472

www. ti. com SPRS612D JUNE 2009 REVISED JULY 2010

6 Device Operating Conditions

6. 1 Absolute Maximum Ratings Over Operating Case Temperature Range (Unless Otherwise Noted) (1) (2) (3)

CVDD CVDD2 DVDD33 DVDD18, AVDDA3, AVDDA4 Supply voltage range: AVDDA1, AVDDA2 DVDD15 DVDDR CVDD1 AVDDA, DVDDD, AVDDT 3. 3-V pins Input voltage (VI) range: RGMII pins DDR2 memory controller pins RIO pins 3. 3-V pins Output voltage (VO) range: RGMII pins DDR2 memory controller pins RIO pins Operating case temperature range, TC: Storage temperature range, Tstg (1) (2) (3) (4) Standard A version

(4)

-0. 5 V to 1. 5 V -0. 5 V to 1. 5 V -0. 5 V to 4. 2 V -0. 5 V to 2. 5 V -0. 5 V to 2. 5 V -0. 5 V to 2. 5 V -0. 5 V to 2. 5 V -0. 5 V to 1. 5 V -0. 5 V to 1. 5 V -0. 5 V to DVDD33 + 0. 5 V -0. 3 V to DVDD15 + 0. 3 V -0. 3 V to DVDD18 + 0. 3 V 0 V to 1. 32 V -0. 3 V to DVDD15 + 0. 3 V -0. 3 V to DVDD18 + 0. 3 V 0 V to 1. 32 V 0°C to 85°C -40°C to 100°C -65°C to 150°C -0. 5 V to DVDD33 + 0. 5 V

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to VSS. Overshoot and undershoot transients due to impedance mismatch on 3. 3-V pins can be up to 30% of the supply voltage for up to 30% of the signal period without significantly impacting reliability. For RGMII and DDR2 pins, limit overshoot/undershoot to 20% of supply voltage for up to 20% of the duty cycle. These period limits assume continuous operation. Extended temperature (A version) range is available only on 500-MHz and 625-MHz devices.

Copyright © 20092010, Texas Instruments Incorporated

Device Operating Conditions Submit Documentation Feedback Product Folder Link(s) :TMS320C6472

111

PRODUCT PREVIEW

TMS320C6472

SPRS612D JUNE 2009 REVISED JULY 2010 www. ti. com

6. 2

Recommended Operating Conditions (1)

PARAMETER 500 MHz MIN 0. 95 1. 05 1. 14 0. 95 1. 05 1. 14 1. 14 3. 135 1. 71 1. 4 0. 7 0. 855 1. 71 1. 71 1. 71 1. 71 1. 14 1. 14 1. 14 1. 35 2. 0 0. 7 * DVDD33 VREFHSTL + 0. 10 VREFSSTL + 0. 125 -0. 5 -0. 5 -0. 3 -0. 3 3. 3-V pins (except I2C pins) 0. 9 1. 8 1. 8 1. 8 1. 8 1. 2 1. 2 1. 2 1. 5/1. 8 625 MHz 700 MHz 500 MHz NOM 1. 0 1. 1 1. 2 1. 0 1. 1 1. 2 1. 2 3. 3 1. 8 MAX UNIT 1. 05 1. 16 1. 26 1. 05 1. 16 1. 26 1. 26 3. 465 1. 89 1. 9 0. 95 0. 945 1. 89 1. 89 1. 89 1. 89 1. 26 1. 26 1. 26 1. 98 DVDD33 + 0. 5 DVDD33 + 0. 5 DVDD15 + 0. 3 DVDD18 + 0. 3 0. 8 0. 3 * DVDD33 VREFHSTL - 0. 1 VREFSSTL - 0. 125 V V V V V V V V V V V V V V V V

CVDD

Supply voltage, Core

CVDD2 CVDD1 DVDD33 DVDD18 DVDD15 VREFHSTL (0. 5 * DVDD15) VREFSSTL (0. 5 * DVDD18) AVDDA1 AVDDA2 AVDDA3 AVDDA4 DVDDD AVDDA AVDDT DVDDR

Supply voltage, SRIO Core

625 MHz 700 MHz

Supply volttage, 1. 2-V DDR Core Supply voltage, 3. 3-V I/O Supply voltage, 1. 8-V I/O (DDR) Supply voltage, 1. 8-V/1. 5-V I/O (RGMII) Reference voltage, RGMII I/O Reference voltage, DDR2 I/O Analog supply voltage, PLL1 (System PLL) Analog supply voltage, PLL2 (EMAC PLL) Analog supply voltage, PLL3 (DDR PLL) Analog supply voltage, DDR SRIO Digital supply voltage SRIO Analog supply voltage SRIO Termination voltage SRIO Regulator supply voltage

PRODUCT PREVIEW

VIH

High-level input voltage

I2C pins RGMII pins DDR2 memory controller pins 3. 3-V pins (except I2C pins)

V

VIL

Low-level input voltage

I2C pins RGMII pins DDR2 memory controller pins CVDD = CVDD2 = 1. 0 V, CPU frequency = 500 MHz

V

2. 38

PCDD

Core supply power

(2)

CVDD = CVDD2 = 1. 1 V, CPU frequency = 625 MHz CVDD = CVDD2 = 1. 2 V, CPU frequency = 700 MHz

3. 76

W

5. 42

(1) (2)

Operating conditions are at 500 MHz, 625 MHz, or 700 MHz. Assumes the following conditions: CPU utilization 30% DSP/60% control; DDR2 at 30% utilization (266 MHz), 35% writes, 32 bits, 15% bit switching; TSIP0, TSIP1, and TSIP2 at 20% utilization, 15% switching; UTOPIA 50 MHz, 16-bit at 50% utilization, 15% switching EMAC0, 1000 Mbps, RGMII, 50% utilization, 50% switching; EMAC1 disabled; SRIO both lanes disabled; all timers active; HPI disabled; I2C enabled at 10% utilization; room temperature (25°C). The actual power consumption is application-dependent. For more details on core and I/O activity, see the TMS320C6472/TMS320TCI6486 Power Consumption Summary (literature number SPRAAS4). Device Operating Conditions Submit Documentation Feedback Product Folder Link(s) :TMS320C6472

Copyright © 20092010, Texas Instruments Incorporated

112

TMS320C6472

www. ti. com SPRS612D JUNE 2009 REVISED JULY 2010

Recommended Operating Conditions (continued)

PARAMETER 3. 3-V Supply (DVDD33) 1. 8-V Supplies, including PLLs (DVDD18, AVDDA1, AVDDA2, AVDDA3, AVDDA4 1. 5-V Supplies (DVDD15, DVDDR) 1. 2-V Supplies (CVDD1, AVDDA, DVDDD, AVDDT) MIN NOM 0. 2 MAX UNIT

0. 26 W 0. 05 0. 28

PDDD

I/O supply power (2)

Copyright © 20092010, Texas Instruments Incorporated

Device Operating Conditions Submit Documentation Feedback Product Folder Link(s) :TMS320C6472

113

PRODUCT PREVIEW

TMS320C6472

SPRS612D JUNE 2009 REVISED JULY 2010 www. ti. com

6. 3

Electrical Characteristics Over Recommended Ranges of Supply Voltage and Operating Case Temperature (Unless Otherwise Noted)

PARAMETER 3. 3 V pins (except I2C pins) I2C pins TEST CONDITIONS (1) DVDD33 = MIN, IOH = MAX DVDD33 = MIN, IOH = MAX MIN 0. 8 * DVDD33 0. 8 * DVDD33 DVDD15 - 0. 4 DVDD18 - 0. 4 DVDD33 = MIN, IOL = MAX Pulled up to 3. 3 V, 3 mA sink current 0. 4 0. 4 0. 4 0. 4 VI = VSS to DVDD33, pins without internal pull-up or pull-down resistor 3. 3-V pins (except I2C pins) VI = VSS to DVDD33, pins with internal pull-up resistor VI = VSS to DVDD33, pins with internal pull-down resistor I2C pins RGMII pins DDR2 memory controller pins E Class Buffers EMU[18:0] and all 3. 3-V Ethernet, except MCRS0_RMCRSDV0, MCOL0, GMDIO, and GMDCLK D Class Buffers GPIO[15:0], TDO, HOUT, and SYSCLKOUT 0. 1 * DVDD33 VI 0. 9 * DVDD33 TYP MAX UNIT V V V V V V V V

VOH

High-level ouput voltage RGMII pins DDR2 memory controller pins 3. 3-V pins (except I2C pins) I2C pins

VOL

Low-level ouput voltage RGMII pins DDR2 memory controller pins

-1

1

uA

PRODUCT PREVIEW

50

100

400

uA

II

Input current (DC)

-400

-100

-50

uA

-10 -1 -1

10 1 1

uA uA uA

-7

mA

-3

mA

IOH

High-level output current

C Class Buffers - HPI, TSIP, UTOPIA, BOOTACTIVE, WDOUT, RESETSTAT, TIMO2, MCRS0_RMCRSDV0, MCOL0, GMDIO, and GMDCLK RGMII pins DDR pins

-3

mA

-8 -13. 4

mA mA

(1) 114

For test conditions shown as MIN, MAX, or NOM, use the appropriate value specified in the recommended operating conditions table. Device Operating Conditions Submit Documentation Feedback Product Folder Link(s) :TMS320C6472

Copyright © 20092010, Texas Instruments Incorporated

TMS320C6472

www. ti. com SPRS612D JUNE 2009 REVISED JULY 2010

Electrical Characteristics Over Recommended Ranges of Supply Voltage and Operating Case Temperature (Unless Otherwise Noted) (continued)

PARAMETER E Class Buffers EMU[18:0] and all 3. 3-V Ethernet, except MCRS0_RMCRSDV0, MCOL0, GMDIO, and GMDCLK D Class Buffers GPIO[15:0], TDO, HOUT, and SYSCLKOUT IOL Low-level output current C Class Buffers - HPI, TSIP, UTOPIA, BOOTACTIVE, WDOUT, RESETSTAT, TIMO2, MCRS0_RMCRSDV0, MCOL0, GMDIO, and GMDCLK RGMII pins DDR pins 3. 3-V pins IOZ Off-state output current RGMII pins DDR pins commercial temperature extended temperature (2) -10 -10 -10 0 -40 TEST CONDITIONS (1) MIN TYP MAX UNIT

7

mA

3

mA

3

mA

8 13. 4 20 10 10 85

mA mA uA uA uA

TC

Operating case temperature

°C 100

(2)

Extended temperature (A) range is available only on 500-MHz and 625-MHz devices.

Copyright © 20092010, Texas Instruments Incorporated

Device Operating Conditions Submit Documentation Feedback Product Folder Link(s) :TMS320C6472

115

PRODUCT PREVIEW

TMS320C6472

SPRS612D JUNE 2009 REVISED JULY 2010 www. ti. com

7 C64x+ Peripheral Information and Electrical Specifications

7. 1 Parameter Information

Tester Pin Electronics 42 W 3. 5 nH Transmission Line Z0 = 50 W

(A)

Data Sheet Timing Reference Point Output Under Test Device Pin

(A)

4. 0 pF

1. 85 pF

A.

The data sheet provides timing at the device pin. For output timing analysis, the tester pin electronics and its transmission line effects must be taken into account. A transmission line with a delay of 2 ns or longer can be used to produce the desired transmission line effect. The transmission line is intended as a load only. It is not necessary to add or subtract the transmission line delay (2 ns or longer) from the data sheet timings. Input requirements in this data sheet are tested with an input slew rate of 4 Volts per nanosecond (V/ns) at the device pin.

PRODUCT PREVIEW

Figure 7-1. Test Load Circuit for AC Timing Measurements The load capacitance value stated is only for characterization and measurement of AC timing signals. This load capacitance value does not indicate the maximum load the device is capable of driving.

7. 1. 1

3. 3-V Signal Transition Levels

All input and output timing parameters are referenced to 1. 5 V for both "0" and "1" logic levels.

Vref = 1. 5 V

Figure 7-2. Input and Output Voltage Reference Levels for AC Timing Measurements All rise and fall transition timing parameters are referenced to VIL MAX and VIH MIN for input clocks, VOLMAX and VOH MIN for output clocks.

Vref = VIH MIN (or VOH MIN) Vref = VIL MAX (or VOL MAX)

Figure 7-3. Rise and Fall Transition Time Voltage Reference Levels

7. 1. 2

3. 3-V Signal Transition Rates

All timings are tested with an input edge rate of 4 Volts per nanosecond (V/ns).

7. 1. 3

Timing Parameters and Board Routing Analysis

The timing parameter values specified in this data sheet do not include delays by board routings. [. . . ] All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. [. . . ]

TEXAS INSTRUMENTS TMS320C6472 FEATURES 10-2010 (1645 ko)

TEXAS INSTRUMENTS TMS320C6472 FEATURES 10-2010 (1645 ko)