User manual TEXAS INSTRUMENTS TMS320C6748 DATASHEET 08-2010

Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets... DON'T FORGET : ALWAYS READ THE USER GUIDE BEFORE BUYING !!!

If this document matches the user guide, instructions manual or user manual, feature sets, schematics you are looking for, download it now. Lastmanuals provides you a fast and easy access to the user manual TEXAS INSTRUMENTS TMS320C6748. We hope that this TEXAS INSTRUMENTS TMS320C6748 user guide will be useful to you.

Lastmanuals help download the user guide TEXAS INSTRUMENTS TMS320C6748.

Manual abstract: user guide TEXAS INSTRUMENTS TMS320C6748DATASHEET 08-2010

Detailed instructions for use are in the User's Guide.

[. . . ] TMS320C6748

www. ti. com SPRS590B JUNE 2009 REVISED AUGUST 2010

TMS320C6748 Fixed/Floating-Point DSP

Check for Samples: TMS320C6748

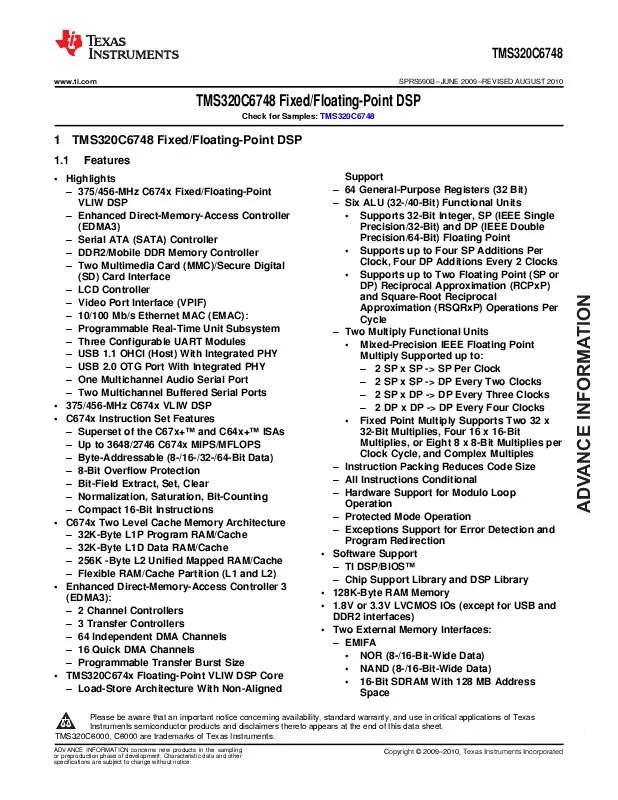

1 TMS320C6748 Fixed/Floating-Point DSP

1. 1

12

Features

Support 64 General-Purpose Registers (32 Bit) Six ALU (32-/40-Bit) Functional Units · Supports 32-Bit Integer, SP (IEEE Single Precision/32-Bit) and DP (IEEE Double Precision/64-Bit) Floating Point · Supports up to Four SP Additions Per Clock, Four DP Additions Every 2 Clocks · Supports up to Two Floating Point (SP or DP) Reciprocal Approximation (RCPxP) and Square-Root Reciprocal Approximation (RSQRxP) Operations Per Cycle Two Multiply Functional Units · Mixed-Precision IEEE Floating Point Multiply Supported up to: 2 SP x SP -> SP Per Clock 2 SP x SP -> DP Every Two Clocks 2 SP x DP -> DP Every Three Clocks 2 DP x DP -> DP Every Four Clocks · Fixed Point Multiply Supports Two 32 x 32-Bit Multiplies, Four 16 x 16-Bit Multiplies, or Eight 8 x 8-Bit Multiplies per Clock Cycle, and Complex Multiples Instruction Packing Reduces Code Size All Instructions Conditional Hardware Support for Modulo Loop Operation Protected Mode Operation Exceptions Support for Error Detection and Program Redirection Software Support TI DSP/BIOSTM Chip Support Library and DSP Library 128K-Byte RAM Memory 1. 8V or 3. 3V LVCMOS IOs (except for USB and DDR2 interfaces) Two External Memory Interfaces: EMIFA · NOR (8-/16-Bit-Wide Data) · NAND (8-/16-Bit-Wide Data) · 16-Bit SDRAM With 128 MB Address Space

· Highlights 375/456-MHz C674x Fixed/Floating-Point VLIW DSP Enhanced Direct-Memory-Access Controller (EDMA3) Serial ATA (SATA) Controller DDR2/Mobile DDR Memory Controller Two Multimedia Card (MMC)/Secure Digital (SD) Card Interface LCD Controller Video Port Interface (VPIF) 10/100 Mb/s Ethernet MAC (EMAC): Programmable Real-Time Unit Subsystem Three Configurable UART Modules USB 1. 1 OHCI (Host) With Integrated PHY USB 2. 0 OTG Port With Integrated PHY One Multichannel Audio Serial Port Two Multichannel Buffered Serial Ports · 375/456-MHz C674x VLIW DSP · C674x Instruction Set Features Superset of the C67x+TM and C64x+TM ISAs Up to 3648/2746 C674x MIPS/MFLOPS Byte-Addressable (8-/16-/32-/64-Bit Data) 8-Bit Overflow Protection Bit-Field Extract, Set, Clear Normalization, Saturation, Bit-Counting Compact 16-Bit Instructions · C674x Two Level Cache Memory Architecture 32K-Byte L1P Program RAM/Cache 32K-Byte L1D Data RAM/Cache 256K -Byte L2 Unified Mapped RAM/Cache Flexible RAM/Cache Partition (L1 and L2) · Enhanced Direct-Memory-Access Controller 3 (EDMA3): 2 Channel Controllers 3 Transfer Controllers 64 Independent DMA Channels 16 Quick DMA Channels Programmable Transfer Burst Size · TMS320C674x Floating-Point VLIW DSP Core Load-Store Architecture With Non-Aligned

1

·

· · ·

2

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. TMS320C6000, C6000 are trademarks of Texas Instruments.

Copyright © 20092010, Texas Instruments Incorporated

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

ADVANCE INFORMATION

TMS320C6748

SPRS590B JUNE 2009 REVISED AUGUST 2010 www. ti. com

·

· · ·

· ·

·

· ·

·

·

DDR2/Mobile DDR Memory Controller · 16-Bit DDR2 SDRAM With 512 MB Address Space or · 16-Bit mDDR SDRAM With 256 MB Address Space Three Configurable 16550 type UART Modules: With Modem Control Signals 16-byte FIFO 16x or 13x Oversampling Option LCD Controller Two Serial Peripheral Interfaces (SPI) Each With Multiple Chip-Selects Two Multimedia Card (MMC)/Secure Digital (SD) Card Interface with Secure Data I/O (SDIO) Interfaces Two Master/Slave Inter-Integrated Circuit (I2C BusTM) One Host-Port Interface (HPI) With 16-Bit-Wide Muxed Address/Data Bus For High Bandwidth Programmable Real-Time Unit Subsystem (PRUSS) Two Independent Programmable Realtime Unit (PRU) Cores · 32-Bit Load/Store RISC architecture · 4K Byte instruction RAM per core · 512 Bytes data RAM per core · PRU Subsystem (PRUSS) can be disabled via software to save power · Register 30 of each PRU is exported from the subsystem in addition to the normal R31 output of the PRU cores. Standard power management mechanism · Clock gating · Entire subsystem under a single PSC clock gating domain Dedicated interrupt controller Dedicated switched central resource USB 1. 1 OHCI (Host) With Integrated PHY (USB1) USB 2. 0 OTG Port With Integrated PHY (USB0) USB 2. 0 High-/Full-Speed Client USB 2. 0 High-/Full-/Low-Speed Host End Point 0 (Control) End Points 1, 2, 3, 4 (Control, Bulk, Interrupt or ISOC) Rx and Tx One Multichannel Audio Serial Port: Two Clock Zones and 16 Serial Data Pins Supports TDM, I2S, and Similar Formats DIT-Capable FIFO buffers for Transmit and Receive Two Multichannel Buffered Serial Ports: Supports TDM, I2S, and Similar Formats AC97 Audio Codec Interface

TMS320C6748 Fixed/Floating-Point DSP

·

·

·

·

· · ·

·

·

·

Telecom Interfaces (ST-Bus, H100) 128-channel TDM FIFO buffers for Transmit and Receive 10/100 Mb/s Ethernet MAC (EMAC): IEEE 802. 3 Compliant MII Media Independent Interface RMII Reduced Media Independent Interface Management Data I/O (MDIO) Module Video Port Interface (VPIF): Two 8-bit SD (BT. 656), Single 16-bit or Single Raw (8-/10-/12-bit) Video Capture Channels Two 8-bit SD (BT. 656), Single 16-bit Video Display Channels Universal Parallel Port (uPP): High-Speed Parallel Interface to FPGAs and Data Converters Data Width on Each of Two Channels is 8- to 16-bit Inclusive Single Data Rate or Dual Data Rate Transfers Supports Multiple Interfaces with START, ENABLE and WAIT Controls Serial ATA (SATA) Controller: Supports SATA I (1. 5 Gbps) and SATA II (3. 0 Gbps) Supports all SATA Power Management Features Hardware-Assisted Native Command Queueing (NCQ) for up to 32 Entries Supports Port Multiplier and Command-Based Switching Real-Time Clock With 32 KHz Oscillator and Separate Power Rail Three 64-Bit General-Purpose Timers (Each configurable as Two 32-Bit Timers) One 64-bit General-Purpose/Watchdog Timer (Configurable as Two 32-bit General-Purpose Timers) Two Enhanced Pulse Width Modulators (eHRPWM): Dedicated 16-Bit Time-Base Counter With Period And Frequency Control 6 Single Edge, 6 Dual Edge Symmetric or 3 Dual Edge Asymmetric Outputs Dead-Band Generation PWM Chopping by High-Frequency Carrier Trip Zone Input Three 32-Bit Enhanced Capture Modules (eCAP): Configurable as 3 Capture Inputs or 3 Auxiliary Pulse Width Modulator (APWM) outputs Single Shot Capture of up to Four Event Time-Stamps 361-Ball Pb-Free Plastic Ball Grid Array (PBGA)

Copyright © 20092010, Texas Instruments Incorporated

ADVANCE INFORMATION

2

Submit Documentation Feedback Product Folder Link(s): TMS320C6748

TMS320C6748

www. ti. com SPRS590B JUNE 2009 REVISED AUGUST 2010

[ZCE Suffix], 0. 65-mm Ball Pitch · 361-Ball Pb-Free Plastic Ball Grid Array (PBGA) [ZWT Suffix], 0. 80-mm Ball Pitch · Commercial, Extended or Industrial

Temperature · Community Resources TI E2E Community TI Embedded Processors Wiki

Copyright © 20092010, Texas Instruments Incorporated

TMS320C6748 Fixed/Floating-Point DSP Submit Documentation Feedback Product Folder Link(s): TMS320C6748

3

ADVANCE INFORMATION

TMS320C6748

SPRS590B JUNE 2009 REVISED AUGUST 2010 www. ti. com

1. 2

Trademarks

DSP/BIOS, TMS320C6000, C6000, TMS320, TMS320C62x, and TMS320C67x are trademarks of Texas Instruments. [. . . ] Additional layers may be added to the PCB stack up to accommodate other circuitry or to reduce the size of the PCB footprint. Complete stack up specifications are provided in Table 6-27. Device Minimum PCB Stack Up

Layer 1 2 3 4 5 6 Type Signal Plane Plane Signal Plane Signal Description Top Routing Mostly Horizontal Ground Power Internal Routing Ground Bottom Routing Mostly Vertical

Table 6-27. Parameter 1 2 3 4 5 6 7 8 8 9 10 11 12 13 (1) (2) (3) PCB Routing/Plane Layers Signal Routing Layers Full ground layers under DDR2/mDDR routing region Number of ground plane cuts allowed within DDR routing region Number of ground reference planes required for each DDR2/mDDR routing layer Number of layers between DDR2/mDDR routing layer and reference ground plane PCB Routing Feature Size PCB Trace Width w PCB BGA escape via pad size PCB BGA escape via hole size DSP Device BGA pad size DDR2/mDDR Device BGA pad size Single Ended Impedance, Zo Impedance Control 50 Z-5 Z 75 Z+5 See Note

(3)

Min 6 3 2

Typ

Max

Unit

Notes

0 1 0 4 4 18 8 Mils Mils Mils Mils See Note See Note

(1) (2)

Please refer to the Flip Chip Ball Grid Array Package Reference Guide (SPRU811) for device BGA pad size. Please refer to the DDR2/mDDR device manufacturer documentation for the DDR2/mDDR device BGA pad size. Z is the nominal singled ended impedance selected for the PCB specified by item 12.

Copyright © 20092010, Texas Instruments Incorporated

Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): TMS320C6748

125

ADVANCE INFORMATION

6. 11. 3. 3 PCB Stackup

TMS320C6748

SPRS590B JUNE 2009 REVISED AUGUST 2010 www. ti. com

6. 11. 3. 4 Placement Figure 6-19 shows the required placement for the device as well as the DDR2/mDDR devices. The dimensions for Figure 6-20 are defined in Table 6-28. The placement does not restrict the side of the PCB that the devices are mounted on. The ultimate purpose of the placement is to limit the maximum trace lengths and allow for proper routing space. For single-memory DDR2/mDDR systems, the second DDR2/mDDR device is omitted from the placement.

X A1 Y OFFSET Y DDR2/mDDR Device Y OFFSET A1

Recommended DDR2/mDDR Device Orientation

Figure 6-20. C6748 and DDR2/mDDR Device Placement Table 6-28. 1 2 3 4 (1) (2) (3) (4) (5) Parameter X Y Y Offset Clearance from non-DDR2/mDDR signal to DDR2/mDDR Keepout Region 4 Min Max 1750 1280 650 Unit Notes

(1) (2)

DDR2/mDDR Controller

ADVANCE INFORMATION

Mils See Notes Mils See Notes Mils See Notes w

(4)

,

(1) (2)

, .

(1) (2) (3)

,

See Note

(5)

See Figure 6-20 for dimension definitions. Measurements from center of device to center of DDR2/mDDR device. For single memory systems it is recommended that Y Offset be as small as possible. w = PCB trace width as defined in Table 6-27 Non-DDR2/mDDR signals allowed within DDR2/mDDR keepout region provided they are separated from DDR2/mDDR routing layers by a ground plane.

126

Peripheral Information and Electrical Specifications Copyright © 20092010, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Link(s): TMS320C6748

TMS320C6748

www. ti. com SPRS590B JUNE 2009 REVISED AUGUST 2010

6. 11. 3. 5 DDR2/mDDR Keep Out Region The region of the PCB used for the DDR2/mDDR circuitry must be isolated from other signals. The DDR2/mDDR keep out region is defined for this purpose and is shown in Figure 6-21. The size of this region varies with the placement and DDR routing. Additional clearances required for the keep out region are shown in Table 6-28.

A1

DDR2/mDDR Device

A1

DDR2/mDDR Controller

Region should encompass all DDR2/mDDR circuitry and varies depending on placement. Non-DDR2/mDDR signals should not be routed on the DDR signal layers within the DDR2/mDDR keep out region. Non-DDR2/mDDR signals may be routed in the region provided they are routed on layers separated from DDR2/mDDR signal layers by a ground layer. No breaks should be allowed in the reference ground layers in this region. In addition, the 1. 8 V power plane should cover the entire keep out region.

Figure 6-21. DDR2/mDDR Keepout Region

Copyright © 20092010, Texas Instruments Incorporated

Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): TMS320C6748

127

ADVANCE INFORMATION

TMS320C6748

SPRS590B JUNE 2009 REVISED AUGUST 2010 www. ti. com

6. 11. 3. 6 Bulk Bypass Capacitors Bulk bypass capacitors are required for moderate speed bypassing of the DDR2/mDDR and other circuitry. [. . . ] All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. [. . . ]

DISCLAIMER TO DOWNLOAD THE USER GUIDE TEXAS INSTRUMENTS TMS320C6748 Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets...manual TEXAS INSTRUMENTS TMS320C6748