Detailed instructions for use are in the User's Guide.

[. . . ] TMS320DM643

www. ti. com SPRS269D FEBRUARY 2005 REVISED OCTOBER 2010

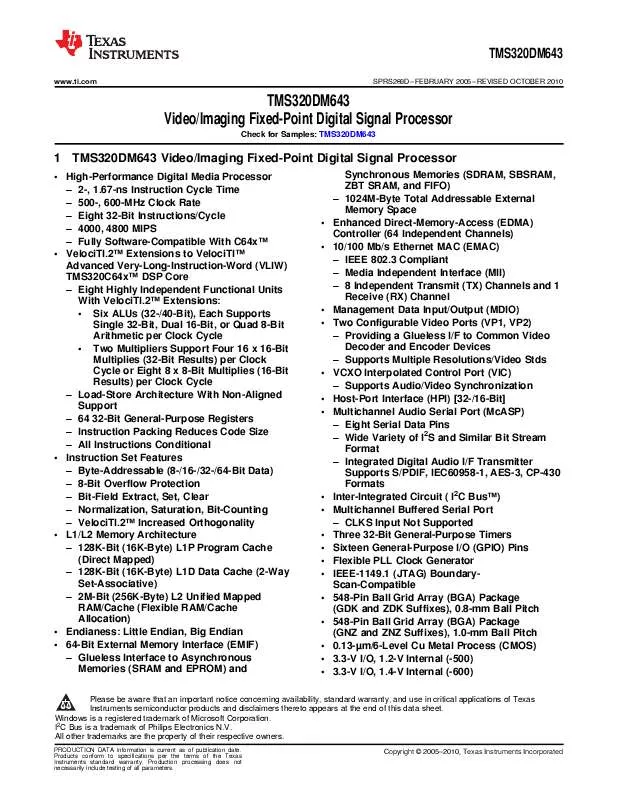

TMS320DM643 Video/Imaging Fixed-Point Digital Signal Processor

Check for Samples: TMS320DM643

1 TMS320DM643 Video/Imaging Fixed-Point Digital Signal Processor

1234

· High-Performance Digital Media Processor 2-, 1. 67-ns Instruction Cycle Time 500-, 600-MHz Clock Rate Eight 32-Bit Instructions/Cycle 4000, 4800 MIPS Fully Software-Compatible With C64xTM · VelociTI. 2TM Extensions to VelociTITM Advanced Very-Long-Instruction-Word (VLIW) TMS320C64xTM DSP Core Eight Highly Independent Functional Units With VelociTI. 2TM Extensions: · Six ALUs (32-/40-Bit), Each Supports Single 32-Bit, Dual 16-Bit, or Quad 8-Bit Arithmetic per Clock Cycle · Two Multipliers Support Four 16 x 16-Bit Multiplies (32-Bit Results) per Clock Cycle or Eight 8 x 8-Bit Multiplies (16-Bit Results) per Clock Cycle Load-Store Architecture With Non-Aligned Support 64 32-Bit General-Purpose Registers Instruction Packing Reduces Code Size All Instructions Conditional · Instruction Set Features Byte-Addressable (8-/16-/32-/64-Bit Data) 8-Bit Overflow Protection Bit-Field Extract, Set, Clear Normalization, Saturation, Bit-Counting VelociTI. 2TM Increased Orthogonality · L1/L2 Memory Architecture 128K-Bit (16K-Byte) L1P Program Cache (Direct Mapped) 128K-Bit (16K-Byte) L1D Data Cache (2-Way Set-Associative) 2M-Bit (256K-Byte) L2 Unified Mapped RAM/Cache (Flexible RAM/Cache Allocation) · Endianess: Little Endian, Big Endian · 64-Bit External Memory Interface (EMIF) Glueless Interface to Asynchronous Memories (SRAM and EPROM) and

1

· ·

· ·

· · ·

· · · · · · · · · · ·

Synchronous Memories (SDRAM, SBSRAM, ZBT SRAM, and FIFO) 1024M-Byte Total Addressable External Memory Space Enhanced Direct-Memory-Access (EDMA) Controller (64 Independent Channels) 10/100 Mb/s Ethernet MAC (EMAC) IEEE 802. 3 Compliant Media Independent Interface (MII) 8 Independent Transmit (TX) Channels and 1 Receive (RX) Channel Management Data Input/Output (MDIO) Two Configurable Video Ports (VP1, VP2) Providing a Glueless I/F to Common Video Decoder and Encoder Devices Supports Multiple Resolutions/Video Stds VCXO Interpolated Control Port (VIC) Supports Audio/Video Synchronization Host-Port Interface (HPI) [32-/16-Bit] Multichannel Audio Serial Port (McASP) Eight Serial Data Pins Wide Variety of I2S and Similar Bit Stream Format Integrated Digital Audio I/F Transmitter Supports S/PDIF, IEC60958-1, AES-3, CP-430 Formats Inter-Integrated Circuit ( I2C BusTM) Multichannel Buffered Serial Port CLKS Input Not Supported Three 32-Bit General-Purpose Timers Sixteen General-Purpose I/O (GPIO) Pins Flexible PLL Clock Generator IEEE-1149. 1 (JTAG) BoundaryScan-Compatible 548-Pin Ball Grid Array (BGA) Package (GDK and ZDK Suffixes), 0. 8-mm Ball Pitch 548-Pin Ball Grid Array (BGA) Package (GNZ and ZNZ Suffixes), 1. 0-mm Ball Pitch 0. 13-µm/6-Level Cu Metal Process (CMOS) 3. 3-V I/O, 1. 2-V Internal (-500) 3. 3-V I/O, 1. 4-V Internal (-600)

2

3

4

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. Windows is a registered trademark of Microsoft Corporation. 2 I C Bus is a trademark of Philips Electronics N. V. All other trademarks are the property of their respective owners.

Copyright © 20052010, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date. [. . . ] Timing Requirements for Reset (see Figure 5-11)

NO. 1 16 17 (1) (2) (3) tw(RST) tsu(boot) th(boot) Width of the RESET pulse Setup time, boot configuration bits valid before RESET high Hold time, boot configuration bits valid after RESET high

(1) (1)

500 600 MIN 250 4E or 4C (2) 4P

(3)

UNIT MAX µs ns ns

AEA[22:19], LENDIAN, and HD5 are the boot configuration pins during device reset. Select the MIN parameter value, whichever value is larger. For example, when running parts at 600 MHz, use P = 1. 67 ns.

Copyright © 20052010, Texas Instruments Incorporated

DM643 Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): TMS320DM643

77

TMS320DM643

SPRS269D FEBRUARY 2005 REVISED OCTOBER 2010 www. ti. com (2) (3)

Table 5-11. Switching Characteristics Over Recommended Operating Conditions During Reset (1) (see Figure 5-11)

NO. 2 3 4 5 6 7 8 9 10 11 14 15 (1) (2) (3) td(RSTL-ECKI) td(RSTH-ECKI) td(RSTL-ECKO1HZ) td(RSTH-ECKO1V) td(RSTL-EMIFZHZ) td(RSTH-EMIFZV) td(RSTL-EMIFHIV) td(RSTH-EMIFHV) td(RSTL-EMIFLIV) td(RSTH-EMIFLV) td(RSTL-ZHZ) td(RSTH-ZV) PARAMETER Delay time, RESET low to AECLKIN synchronized internally Delay time, RESET high to AECLKIN synchronized internally Delay time, RESET low to AECLKOUT1 high impedance Delay time, RESET high to AECLKOUT1 valid Delay time, RESET low to EMIF Z high impedance Delay time, RESET high to EMIF Z valid Delay time, RESET low to EMIF high group invalid Delay time, RESET high to EMIF high group valid Delay time, RESET low to EMIF low group invalid Delay time, RESET high to EMIF low group valid Delay time, RESET low to Z group high impedance Delay time, RESET high to Z group valid 0 2P 8P 2E 8P + 20E 2E 16E 2E 8P + 20E 500 600 MIN 2E 2E 2E 8P + 20E 3P + 4E 8P + 20E MAX 3P + 20E 8P + 20E

UNIT ns ns ns ns ns ns ns ns ns ns ns ns

P = 1/CPU clock frequency in ns. For example, when running parts at 600 MHz, use P = 1. 67 ns. E = the EMIF input clock (AECLKIN, CPU/4 clock, or CPU/6 clock) period in ns for EMIFA. EMIF Z group consists of: AEA[22:3], AED[63:0], ACE[3:0], ABE[7:0], AARE/ASDCAS/ASADS/ASRE, AAWE/ASDWE/ASWE, AAOE/ASDRAS/ASOE, ASOE3, ASDCKE, and APDT EMIF high group consists of: AHOLDA (when the corresponding HOLD input is high) EMIF low group consists of: ABUSREQ; AHOLDA (when the corresponding HOLD input is low) Z group consists of: HD[31:0] and the muxed EMAC output pins, MDCLK, MDIO, CLKX0, FSX0, DX0, CLKR0, FSR0, TOUT0, TOUT1, VDAC/GP0[8], GP0[13, 11, 10, 7:0], HR/W, HDS2, HDS1, HCS, HCNTL1, HAS, HCNTL0, HHWIL (16-bit HPI mode only), HRDY, HINT, VP1D[19:0], and VP2D[19:0].

78

DM643 Peripheral Information and Electrical Specifications Copyright © 20052010, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Link(s): TMS320DM643

TMS320DM643

www. ti. com SPRS269D FEBRUARY 2005 REVISED OCTOBER 2010

CLKOUT4 CLKOUT6 1 RESET 2 AECLKIN 4 AECLKOUT1 AECLKOUT2 6 EMIF Z Group(A)(B) 8 EMIF High Group(A) 10 EMIF Low Group(A) 14 Z Group(A)(B) 17 16 Boot and Device Configuration Inputs(C) A. EMIF Z group consists of: AEA[22:3], AED[63:0], ACE[3:0], ABE[7:0], AARE/ASDCAS/ASADS/ASRE, AAWE/ASDWE/ASWE, and AAOE/ASDRAS/ASOE, ASOE3, ASDCKE, and APDT. EMIF high group consists of: AHOLDA (when the corresponding HOLD input is high) EMIF low group consists of: ABUSREQ; AHOLDA (when the corresponding HOLD input is low) Z group consists of: HD[31:0] and the muxed EMAC output pins, MDCLK, MDIO, CLKX0, FSX0, DX0, CLKR0, FSR0, TOUT0, TOUT1, VDAC/GP0[8], GP0[13, 11, 10, 7:0], HR/W, HDS2, HDS1, HCS, HCNTL1, HAS, HCNTL0, HHWIL (16-bit HPI mode only), HRDY, HINT, VP1D[19:0], and VP2D[19:0]. If AEA[22:19], LENDIAN, and HD5 pins are actively driven, care must be taken to ensure no timing contention between parameters 6, 7, 14, 15, 16, and 17. Boot and Device Configurations Inputs (during reset) include: AEA[22:19], LENDIAN, and HD5. Reset Timing

Copyright © 20052010, Texas Instruments Incorporated

DM643 Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): TMS320DM643

79

TMS320DM643

SPRS269D FEBRUARY 2005 REVISED OCTOBER 2010 www. ti. com

5. 7

Clock PLL

The PLL controller features hardware-configurable PLL multiplier controller, dividers (/2, /4, /6, and /8), and reset controller. The PLL controller accepts an input clock, as determined by the logic state on the CLKMODE[1:0] pins, from the CLKIN pin. The resulting clock outputs are passed to the DSP core, peripherals, and other modules inside the C6000TM DSP.

5. 7. 1

Clock PLL Device-Specific Information

Most of the internal C64xTM DSP clocks are generated from a single source through the CLKIN pin. This source clock either drives the PLL, which multiplies the source clock frequency to generate the internal CPU clock, or bypasses the PLL to become the internal CPU clock. To use the PLL to generate the CPU clock, the external PLL filter circuit must be properly designed. Figure 5-12 shows the external PLL circuitry for either x1 (PLL bypass) or other PLL multiply modes. To minimize the clock jitter, a single clean power supply should power both the C64xTM DSP device and the external clock oscillator circuit. The minimum CLKIN rise and fall times should also be observed. For the input clock timing requirements, see the input and output clocks electricals section. [. . . ] All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. [. . . ]