User manual TEXAS INSTRUMENTS TMS320DM6467 FEATURES 10-2010

Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets... DON'T FORGET : ALWAYS READ THE USER GUIDE BEFORE BUYING !!!

If this document matches the user guide, instructions manual or user manual, feature sets, schematics you are looking for, download it now. Lastmanuals provides you a fast and easy access to the user manual TEXAS INSTRUMENTS TMS320DM6467. We hope that this TEXAS INSTRUMENTS TMS320DM6467 user guide will be useful to you.

Lastmanuals help download the user guide TEXAS INSTRUMENTS TMS320DM6467.

Manual abstract: user guide TEXAS INSTRUMENTS TMS320DM6467FEATURES 10-2010

Detailed instructions for use are in the User's Guide.

[. . . ] TMS320DM6467

www. ti. com SPRS403G DECEMBER 2007 REVISED OCTOBER 2010

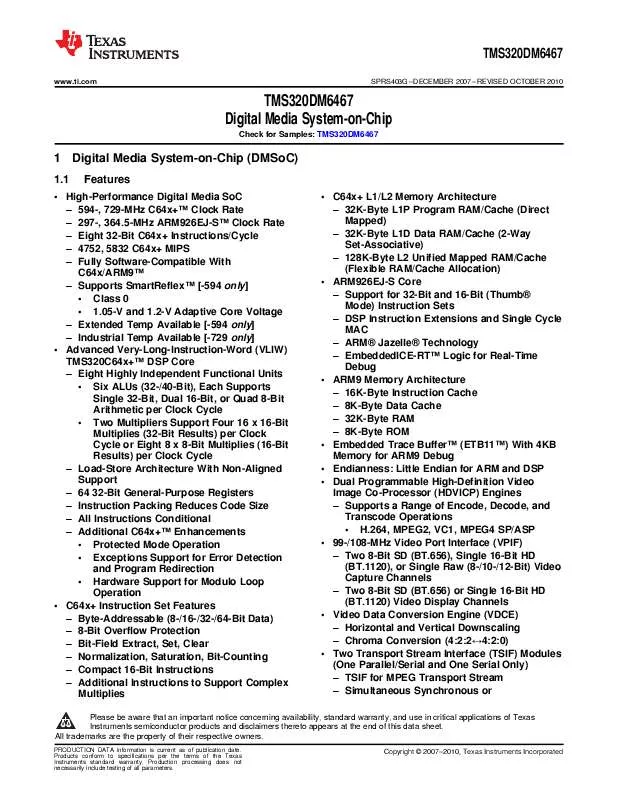

TMS320DM6467 Digital Media System-on-Chip

Check for Samples: TMS320DM6467

1 Digital Media System-on-Chip (DMSoC)

1. 1

12

Features

· C64x+ L1/L2 Memory Architecture 32K-Byte L1P Program RAM/Cache (Direct Mapped) 32K-Byte L1D Data RAM/Cache (2-Way Set-Associative) 128K-Byte L2 Unified Mapped RAM/Cache (Flexible RAM/Cache Allocation) · ARM926EJ-S Core Support for 32-Bit and 16-Bit (Thumb® Mode) Instruction Sets DSP Instruction Extensions and Single Cycle MAC ARM® Jazelle® Technology EmbeddedICE-RTTM Logic for Real-Time Debug · ARM9 Memory Architecture 16K-Byte Instruction Cache 8K-Byte Data Cache 32K-Byte RAM 8K-Byte ROM · Embedded Trace BufferTM (ETB11TM) With 4KB Memory for ARM9 Debug · Endianness: Little Endian for ARM and DSP · Dual Programmable High-Definition Video Image Co-Processor (HDVICP) Engines Supports a Range of Encode, Decode, and Transcode Operations · H. 264, MPEG2, VC1, MPEG4 SP/ASP · 99-/108-MHz Video Port Interface (VPIF) Two 8-Bit SD (BT. 656), Single 16-Bit HD (BT. 1120), or Single Raw (8-/10-/12-Bit) Video Capture Channels Two 8-Bit SD (BT. 656) or Single 16-Bit HD (BT. 1120) Video Display Channels · Video Data Conversion Engine (VDCE) Horizontal and Vertical Downscaling Chroma Conversion (4:2:24:2:0) · Two Transport Stream Interface (TSIF) Modules (One Parallel/Serial and One Serial Only) TSIF for MPEG Transport Stream Simultaneous Synchronous or

· High-Performance Digital Media SoC 594-, 729-MHz C64x+TM Clock Rate 297-, 364. 5-MHz ARM926EJ-STM Clock Rate Eight 32-Bit C64x+ Instructions/Cycle 4752, 5832 C64x+ MIPS Fully Software-Compatible With C64x/ARM9TM Supports SmartReflexTM [-594 only] · Class 0 · 1. 05-V and 1. 2-V Adaptive Core Voltage Extended Temp Available [-594 only] Industrial Temp Available [-729 only] · Advanced Very-Long-Instruction-Word (VLIW) TMS320C64x+TM DSP Core Eight Highly Independent Functional Units · Six ALUs (32-/40-Bit), Each Supports Single 32-Bit, Dual 16-Bit, or Quad 8-Bit Arithmetic per Clock Cycle · Two Multipliers Support Four 16 x 16-Bit Multiplies (32-Bit Results) per Clock Cycle or Eight 8 x 8-Bit Multiplies (16-Bit Results) per Clock Cycle Load-Store Architecture With Non-Aligned Support 64 32-Bit General-Purpose Registers Instruction Packing Reduces Code Size All Instructions Conditional Additional C64x+TM Enhancements · Protected Mode Operation · Exceptions Support for Error Detection and Program Redirection · Hardware Support for Modulo Loop Operation · C64x+ Instruction Set Features Byte-Addressable (8-/16-/32-/64-Bit Data) 8-Bit Overflow Protection Bit-Field Extract, Set, Clear Normalization, Saturation, Bit-Counting Compact 16-Bit Instructions Additional Instructions to Support Complex Multiplies

1

2

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

Copyright © 20072010, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

TMS320DM6467

SPRS403G DECEMBER 2007 REVISED OCTOBER 2010 www. ti. com

·

·

·

·

·

· ·

Asynchronous Input/Output Streams Absolute Time Stamp Detection PID Filter With 7 PID Filter Tables Corresponding Clock Reference Generator (CRGEN) Modules for System Time-Clock Recovery External Memory Interfaces (EMIFs) 297-/310. 5-MHz 32-Bit DDR2 SDRAM Memory Controller With 512M-Byte Address Space (1. 8-V I/O) Asynchronous16-Bit-Wide EMIF (EMIFA) With 128M-Byte Address Reach · Flash Memory Interfaces NOR (8-/16-Bit-Wide Data) NAND (8-/16-Bit-Wide Data) Enhanced Direct-Memory-Access (EDMA) Controller (64 Independent Channels) Programmable Default Burst Size 10/100/1000 Mb/s Ethernet MAC (EMAC) IEEE 802. 3 Compliant (3. 3-V I/O Only) Supports MII and GMII Media Independent Interfaces Management Data I/O (MDIO) Module USB Port With Integrated 2. 0 PHY USB 2. 0 High-/Full-Speed Client USB 2. 0 High-/Full-/Low-Speed Host (Mini-Host, Supporting One External Device) 32-Bit, 33-MHz, 3. 3-V Peripheral Component Interconnect (PCI) Master/Slave Interface Conforms to PCI Specification 2. 3 Two 64-Bit General-Purpose Timers (Each Configurable as Two 32-Bit Timers) One 64-Bit Watchdog Timer

· Three Configurable UART/IrDA/CIR Modules (One With Modem Control Signals) Supports up to 1. 8432 Mbps UART SIR and MIR (0. 576 MBAUD) CIR With Programmable Data Encoding · One Serial Peripheral Interface (SPI) With Two Chip-Selects · Master/Slave Inter-Integrated Circuit (I2C BusTM) · Two Multichannel Audio Serial Ports (McASPs) One Four-Serializer Transmit/Receive Port One Single DIT Transmit Port for S/PDIF · 32-Bit Host Port Interface (HPI) · VLYNQTM Interface (FPGA Interface) · Two Pulse Width Modulator (PWM) Outputs · ATA/ATAPI I/F (ATA/ATAPI-6 Specification) · Up to 33 General-Purpose I/O (GPIO) Pins (Multiplexed With Other Device Functions) · On-Chip ARM ROM Bootloader (RBL) · Individual Power-Saving Modes for ARM/DSP · Flexible PLL Clock Generators · IEEE-1149. 1 (JTAG) BoundaryScan-Compatible · 529-Pin Pb-Free BGA Package (ZUT Suffix), 0. 8-mm Ball Pitch · 0. 09-mm/7-Level Cu Metal Process (CMOS) · 3. 3-V and 1. 8-V I/O, 1. 2-/1. 05-V Internal · Applications: Video Encode/Decode/Transcode/Transrate Digital Media Networked Media Encode/Decode Video Imaging Video Infrastructure Video Conferencing

2

Digital Media System-on-Chip (DMSoC) Submit Documentation Feedback Product Folder Link(s): TMS320DM6467

Copyright © 20072010, Texas Instruments Incorporated

TMS320DM6467

www. ti. com SPRS403G DECEMBER 2007 REVISED OCTOBER 2010

1. 2

Description

The TMS320DM6467 (also referenced as DM6467) leverages TI's DaVinciTM technology to meet the networked media encode and decode digital media processing needs of next-generation embedded devices. [. . . ] 101 = CRGEN0 and CRGEN1 selection enabled. 110 = CRGEN0 selection enabled (muxed with UART2 data). 111 = Reserved (no CRGEN signals enabled). TSIF1 Serial Output Pin Mux Control (see (1), TSSO Signal Muxing). 10 = TS1 output selection enabled (muxed on VP_DOUT pins). 11 = TS1 output selection enabled (muxed on URIN0, UCTS2, PWM0, and PWM1 pins). TSIF1 Serial Input Pin Mux Control (see Section 4. 7. 3. 5, TSIF1 Input Signal Muxing). 01 = TS1 input selection enabled (muxed on UART0 pins). 10 = TS1 input selection enabled (muxed on VP_DOUT pins). 11 = TS1 input selection enabled (muxed on VP_DIN pins). TSIF0 Parallel/Serial Output Pin Mux Control (see Section 4. 7. 3. 4, TSIF0 Output Signal Muxing). 10 = TS0 parallel output muxing enabled (muxed with VP_DIN pins). 11 = TS0 serial output muxing enabled (muxed TS0_DOUT7 with UTXD1). TSIF0 Parallel/Serial Input Pin Mux Control (see Section 4. 7. 3. 3, TSIF0 Input Signal Muxing). 10 = TS0 parallel input muxing enabled (muxed with VP_DIN pins). 11 = TS0 serial input muxing enabled (muxed TS0_DIN7 with URXD1). Note: For proper device operation, when writing to this bit, only a "0" should be written. PCI Function Enable (see Section 4. 7. 3. 1, PCI, HPI, EMIFA and ATA Pin Muxing). Default value is determined by PCIEN boot configuration pin. HPI Function Enable (see Section 4. 7. 3. 1, PCI, HPI, EMIFA and ATA Pin Muxing). ATA Function Enable (see Section 4. 7. 3. 1, PCI, HPI, EMIFA and ATA Pin Muxing). DESCRIPTION

30

STCCK

29

AUDCK1

28 27

AUDCK0 RSV

26:24

CRGMUX

23:22

TSSOMUX

21:20

TSSIMUX

19:18

TSPOMUX

17:16 15:6 5 4:3 2 1 0 (1)

TSPIMUX RESERVED RESERVED RESERVED PCIEN HPIEN ATAEN

IPD = Internal pulldown, IPU = Internal pullup. [. . . ] All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. [. . . ]

DISCLAIMER TO DOWNLOAD THE USER GUIDE TEXAS INSTRUMENTS TMS320DM6467 Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets...manual TEXAS INSTRUMENTS TMS320DM6467