User manual CADENCE DESIGN SYSTEMS ENCOUNTER CONFORMAL EQUIVALENCE CHECKER DATASHEET

Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets... DON'T FORGET : ALWAYS READ THE USER GUIDE BEFORE BUYING !!!

If this document matches the user guide, instructions manual or user manual, feature sets, schematics you are looking for, download it now. Lastmanuals provides you a fast and easy access to the user manual CADENCE DESIGN SYSTEMS ENCOUNTER CONFORMAL EQUIVALENCE CHECKER. We hope that this CADENCE DESIGN SYSTEMS ENCOUNTER CONFORMAL EQUIVALENCE CHECKER user guide will be useful to you.

Lastmanuals help download the user guide CADENCE DESIGN SYSTEMS ENCOUNTER CONFORMAL EQUIVALENCE CHECKER.

Manual abstract: user guide CADENCE DESIGN SYSTEMS ENCOUNTER CONFORMAL EQUIVALENCE CHECKERDATASHEET

Detailed instructions for use are in the User's Guide.

[. . . ] ENC O U N T E R C O N F O R M A L EQU I VA L E N C E C H E C K E R

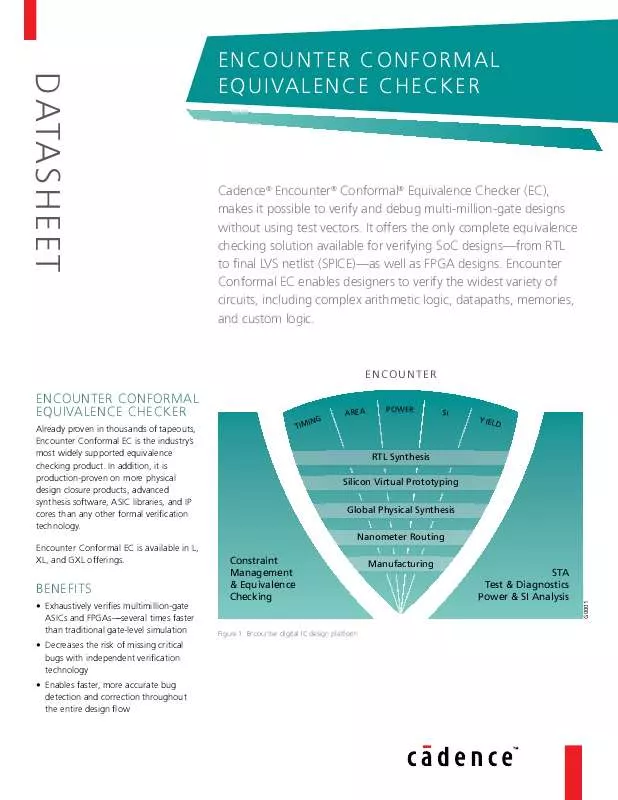

Figure 1: Encounter digital IC design platform

· Decreases the risk of missing critical bugs with independent verification technology · Enables faster, more accurate bug detection and correction throughout the entire design flow

G0001

DATASHEET

ENCOUNTER CONFORMAL EQUIVALENCE CHECKER

Already proven in thousands of tapeouts, Encounter Conformal EC is the industry's most widely supported equivalence checking product. In addition, it is production-proven on more physical design closure products, advanced synthesis software, ASIC libraries, and IP cores than any other formal verification technology. Encounter Conformal EC is available in L, XL, and GXL offerings.

Cadence® Encounter® Conformal® Equivalence Checker (EC), makes it possible to verify and debug multi-million-gate designs without using test vectors. [. . . ] The end result is a safer verification solution. · Clock domain crossing checks Recognize FIFO synchronizers automatically Validate synchronization structure Verify data stability · Semantic checks--Verify synthesis assumptions and find conditions that may create mismatches between RTL and gate-level simulations

Design Flow Independence

Encounter Conformal EC L provides an independent audit of the design process to eliminate the risks associated with sharing technologies across design implementation and design verification products. The tool includes technologies developed independently from the design flow, including production-proven HDL parsing, synthesis, mapping, optimization, and datapath algorithms. Using Encounter Conformal EC L ensures that the maximum number of design bugs will be caught.

FEATURES

ENCOUNTER CONFORMAL EQUIVALENCE CHECKER L

Encounter Conformal EC L combines extended functional checks with core equivalence checking technology.

E N C O U N T E R CONFORMAL EQUIVALENCE CHECKER

w w w. c a d e n ce. com

compares circuitry that has gone through expression optimization and automatically verifies multipliers with standard architectures and dynamic structures · Advanced pipelining check--Verifies proper implementation of pipelined designs · Carry-save verification capability--Allows verification of circuits containing carrysave transformations introduced during optimization for sequence of adders, multipliers, and registers

Final Circuit Verification

Encounter Conformal EC XL is the only verification product that enables a complete verification solution from RTL to final layout. It functionally compares a SPICE netlist created for LVS or extracted from GDS to the RTL or gate model. This process ensures that the circuit on silicon has the same logic function that was designed and verified.

Smart Setup and Diagnosis

Figure 3: Encounter Conformal EC has an easy-to-use GUI with extensive diagnosis and debugging capabilities

· Structural checks--Include bus checks for data conflicts, set-reset exclusivity checks, and multiport latch contention checks

using test vectors. It can handle a wide variety of datapath structures required for high-performance designs. · Automatic flat datapath module verification--Enables easy verification without manually specifying boundaries or architectures in the flattened netlist; automatically verifies merged operators;

ENCOUNTER CONFORMAL EQUIVALENCE CHECKER XL

In addition to all the features provided by Encounter Conformal EC L, Encounter Conformal EC XL offers automated checking of complex datapaths. It also extends equivalence checking to final place-and-route netlist.

Encounter Conformal EC XL includes a set of intelligent `analyze' commands to ease setup and diagnosis. For example, `analyze setup' investigates the current environment and automatically remedies common setup issues sometimes experienced by new users. In tandem, `analyze nonequivalent' can be invoked if non-equivalences are encountered. The command then presents a one-line answer as to what is wrong.

RTL design

Equivalence checking

Abstraction

SPICE reference netlist

Datapath Synthesis Verification

Datapath optimization can create designs that are difficult to formally verify because of complex arithmetic operations. Designers have been relying on simulation to verify datapath blocks, but simulation runtimes are exceedingly long and the results can be incomplete. [. . . ] A Verilog gate logic model of the abstracted circuit can be used for: · Equivalence checking · Fault grading--Preserves the circuit hierarchy and structure for maximum debugging efficiency

For more information Email us at icinfo@cadence. com or visit www. cadence. com.

© 2008 Cadence Design Systems, Inc. Cadence, Conformal, Encounter, and Verilog are registered trademarks, and the Cadence logo is a trademark of Cadence Design Systems, Inc. All others are properties of their respective holders. [. . . ]

DISCLAIMER TO DOWNLOAD THE USER GUIDE CADENCE DESIGN SYSTEMS ENCOUNTER CONFORMAL EQUIVALENCE CHECKER Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets...manual CADENCE DESIGN SYSTEMS ENCOUNTER CONFORMAL EQUIVALENCE CHECKER