User manual TEXAS INSTRUMENTS AM1802 ARM MICROPROCESSOR FEATURES 11-2010

Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets... DON'T FORGET : ALWAYS READ THE USER GUIDE BEFORE BUYING !!!

If this document matches the user guide, instructions manual or user manual, feature sets, schematics you are looking for, download it now. Lastmanuals provides you a fast and easy access to the user manual TEXAS INSTRUMENTS AM1802 ARM MICROPROCESSOR. We hope that this TEXAS INSTRUMENTS AM1802 ARM MICROPROCESSOR user guide will be useful to you.

Lastmanuals help download the user guide TEXAS INSTRUMENTS AM1802 ARM MICROPROCESSOR.

Manual abstract: user guide TEXAS INSTRUMENTS AM1802 ARM MICROPROCESSORFEATURES 11-2010

Detailed instructions for use are in the User's Guide.

[. . . ] AM1802

www. ti. com SPRS710 NOVEMBER 2010

AM1802 ARM Microprocessor

Check for Samples: AM1802

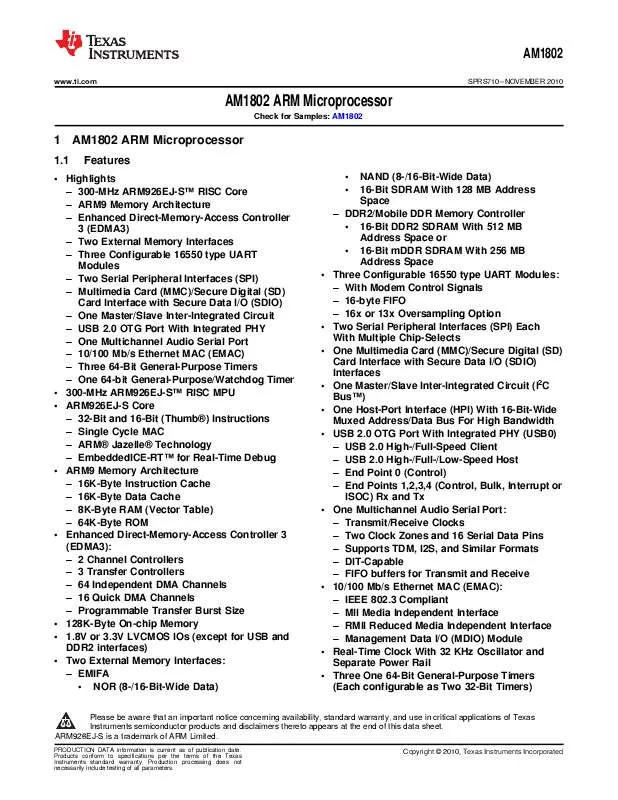

1 AM1802 ARM Microprocessor

1. 1

12

Features

NAND (8-/16-Bit-Wide Data) 16-Bit SDRAM With 128 MB Address Space DDR2/Mobile DDR Memory Controller · 16-Bit DDR2 SDRAM With 512 MB Address Space or · 16-Bit mDDR SDRAM With 256 MB Address Space Three Configurable 16550 type UART Modules: With Modem Control Signals 16-byte FIFO 16x or 13x Oversampling Option Two Serial Peripheral Interfaces (SPI) Each With Multiple Chip-Selects One Multimedia Card (MMC)/Secure Digital (SD) Card Interface with Secure Data I/O (SDIO) Interfaces One Master/Slave Inter-Integrated Circuit (I2C BusTM) One Host-Port Interface (HPI) With 16-Bit-Wide Muxed Address/Data Bus For High Bandwidth USB 2. 0 OTG Port With Integrated PHY (USB0) USB 2. 0 High-/Full-Speed Client USB 2. 0 High-/Full-/Low-Speed Host End Point 0 (Control) End Points 1, 2, 3, 4 (Control, Bulk, Interrupt or ISOC) Rx and Tx One Multichannel Audio Serial Port: Transmit/Receive Clocks Two Clock Zones and 16 Serial Data Pins Supports TDM, I2S, and Similar Formats DIT-Capable FIFO buffers for Transmit and Receive 10/100 Mb/s Ethernet MAC (EMAC): IEEE 802. 3 Compliant MII Media Independent Interface RMII Reduced Media Independent Interface Management Data I/O (MDIO) Module Real-Time Clock With 32 KHz Oscillator and Separate Power Rail Three One 64-Bit General-Purpose Timers (Each configurable as Two 32-Bit Timers) · ·

· Highlights 300-MHz ARM926EJ-STM RISC Core ARM9 Memory Architecture Enhanced Direct-Memory-Access Controller 3 (EDMA3) Two External Memory Interfaces Three Configurable 16550 type UART Modules Two Serial Peripheral Interfaces (SPI) Multimedia Card (MMC)/Secure Digital (SD) Card Interface with Secure Data I/O (SDIO) One Master/Slave Inter-Integrated Circuit USB 2. 0 OTG Port With Integrated PHY One Multichannel Audio Serial Port 10/100 Mb/s Ethernet MAC (EMAC) Three 64-Bit General-Purpose Timers One 64-bit General-Purpose/Watchdog Timer · 300-MHz ARM926EJ-STM RISC MPU · ARM926EJ-S Core 32-Bit and 16-Bit (Thumb®) Instructions Single Cycle MAC ARM® Jazelle® Technology EmbeddedICE-RTTM for Real-Time Debug · ARM9 Memory Architecture 16K-Byte Instruction Cache 16K-Byte Data Cache 8K-Byte RAM (Vector Table) 64K-Byte ROM · Enhanced Direct-Memory-Access Controller 3 (EDMA3): 2 Channel Controllers 3 Transfer Controllers 64 Independent DMA Channels 16 Quick DMA Channels Programmable Transfer Burst Size · 128K-Byte On-chip Memory · 1. 8V or 3. 3V LVCMOS IOs (except for USB and DDR2 interfaces) · Two External Memory Interfaces: EMIFA · NOR (8-/16-Bit-Wide Data)

1

·

· ·

· · ·

·

·

· ·

2

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. ARM926EJ-S is a trademark of ARM Limited.

Copyright © 2010, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

AM1802

SPRS710 NOVEMBER 2010 www. ti. com

· One 64-bit General-Purpose/Watchdog Timer (Configurable as Two 32-bit General-Purpose Timers) · 361-Ball Pb-Free Plastic Ball Grid Array (PBGA) [ZWT Suffix], 0. 80-mm Ball Pitch

· Industrial Temperature · Community Resources TI E2E Community TI Embedded Processors Wiki

2

AM1802 ARM Microprocessor Submit Documentation Feedback Product Folder Link(s): AM1802

Copyright © 2010, Texas Instruments Incorporated

AM1802

www. ti. com SPRS710 NOVEMBER 2010

1. 2

Trademarks

All trademarks are the property of their respective owners.

Copyright © 2010, Texas Instruments Incorporated

AM1802 ARM Microprocessor Submit Documentation Feedback Product Folder Link(s): AM1802

3

AM1802

SPRS710 NOVEMBER 2010 www. ti. com

1. 3

Description

The device is a Low-power applications processor based on ARM926EJ-STM. [. . . ] 1 2 3 4 5 6 7 8 9 10 11 Parameter Center to Center CK-CKN Spacing CK A to B/A to C Skew Length Mismatch CK B to C Skew Length Mismatch Center to center CK to other DDR2/mDDR trace spacing CK/ADDR_CTRL nominal trace length ADDR_CTRL to CK Skew Length Mismatch ADDR_CTRL to ADDR_CTRL Skew Length Mismatch Center to center ADDR_CTRL to other DDR2/mDDR trace spacing Center to center ADDR_CTRL to other ADDR_CTRL trace spacing ADDR_CTRL A to B/A to C Skew Length Mismatch ADDR_CTRL B to C Skew Length Mismatch 4w 3w

(1) (1) (1)

Min

DDR2/mDDR Controller

Typ

B

Max 2w

(1)

Unit See Note Mils Mils See Note See Note

Notes

(2) (3)

25 25 4w

(2) (4)

CACLM-50

CACLM

CACLM+50 100 100

Mils Mils Mils

See Note

See Note See Note 100 100 Mils Mils See Note

(2) (2) (3)

(1) (2) (3) (4)

w = PCB trace width as defined in Table 5-27. Center to center spacing is allowed to fall to minimum (w) for up to 500 mils of routed length to accommodate BGA escape and routing congestion. Series terminator, if used, should be located closest to device. CACLM is the longest Manhattan distance of the CK and ADDR_CTRL net classes.

96

Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): AM1802

Copyright © 2010, Texas Instruments Incorporated

AM1802

www. ti. com SPRS710 NOVEMBER 2010

Figure 5-22 shows the topology and routing for the DQS and D net class; the routes are point to point. Skew matching across bytes is not needed nor recommended.

T A1

T A1 E1

Figure 5-22. DQS and D Routing and Topology Table 5-35. 1 2 3 4 5 6 (1) (2) (3) (4) (5) (6) Parameter Center to center DQS to other DDR2/mDDR trace spacing DQS/D nominal trace length D to DQS Skew Length Mismatch D to D Skew Length Mismatch Center to center D to other DDR2/mDDR trace spacing Center to Center D to other D trace spacing 4w 3w

(1)

Min 4w

(1)

DDR2/mDDR Controller

E0

Typ

Max

Unit

Notes See Note

(2)

DQLM-50

DQLM

DQLM+50 100 100

Mils Mils Mils

See Notes See Note See Note

(3) (4)

,

(4) (4) (2) (5)

See Notes See Notes

,

(1)

(6) (2)

,

w = PCB trace width as defined in Table 5-27. Center to center spacing is allowed to fall to minimum (w) for up to 500 mils of routed length to accommodate BGA escape and routing congestion. Series terminator, if used, should be located closest to DDR. There is no need and it is not recommended to skew match across data bytes, i. e. , from DQS0 and data byte 0 to DQS1 and data byte 1. D's from other DQS domains are considered other DDR2/mDDR trace. DQLM is the longest Manhattan distance of each of the DQS and D net class.

Copyright © 2010, Texas Instruments Incorporated

Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): AM1802

97

AM1802

SPRS710 NOVEMBER 2010 www. ti. com

Figure 5-23 shows the routing for the DQGATE net class. Table 5-36 contains the routing specification.

A1

T

A1

Figure 5-23. 1 2 3 4 (1) (2) (3) Parameter DQGATE Length F Center to center DQGATE to any other trace spacing DQS/D nominal trace length DQGATE Skew CKB0B1 is the sum of the length of the CK net plus the average length of the DQS0 and DQS1 nets. w = PCB trace width as defined in Table 5-27. Skew from CKB0B1 4w

(2)

Min

DDR2/mDDR Controller

F

T

Typ CKB0B1

Max

Unit

Notes See Note

(1)

DQLM-50

DQLM

DQLM+50 100

Mils Mils See Note

(3)

5. 11. 3. 12 MDDR/DDR2 Boundary Scan Limitations Due to DDR implementation and timing restrictions, it was not possible to place boundary scan cells between core logic and the IO like boundary scan cells for other IO. Instead, the boundary scan cells are tapped-off to the DDR PHY and there is the equivalent of a multiplexer inside the DDR PHY which selects between functional and boundary scan paths. The implication for boundary scan is that the DDR pins will not support the SAMPLE function of the output enable cells on the DDR pins and this is a violation of IEEE 1149. 1. Full EXTEST and PRELOAD capability is still available.

98

Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): AM1802

Copyright © 2010, Texas Instruments Incorporated

AM1802

www. ti. com SPRS710 NOVEMBER 2010

5. 12 Memory Protection Units

The MPU performs memory protection checking. It receives requests from a bus master in the system and checks the address against the fixed and programmable regions to see if the access is allowed. If allowed, the transfer is passed unmodified to its output bus (to the targeted address). If the transfer is illegal (fails the protection check) then the MPU does not pass the transfer to the output bus but rather services the transfer internally back to the input bus (to prevent a hang) returning the fault status to the requestor as well as generating an interrupt about the fault. [. . . ] All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. [. . . ]

DISCLAIMER TO DOWNLOAD THE USER GUIDE TEXAS INSTRUMENTS AM1802 ARM MICROPROCESSOR Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets...manual TEXAS INSTRUMENTS AM1802 ARM MICROPROCESSOR