User manual TEXAS INSTRUMENTS TMS320C6455 DATASHEET 09-2010

Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets... DON'T FORGET : ALWAYS READ THE USER GUIDE BEFORE BUYING !!!

If this document matches the user guide, instructions manual or user manual, feature sets, schematics you are looking for, download it now. Lastmanuals provides you a fast and easy access to the user manual TEXAS INSTRUMENTS TMS320C6455. We hope that this TEXAS INSTRUMENTS TMS320C6455 user guide will be useful to you.

Lastmanuals help download the user guide TEXAS INSTRUMENTS TMS320C6455.

Manual abstract: user guide TEXAS INSTRUMENTS TMS320C6455DATASHEET 09-2010

Detailed instructions for use are in the User's Guide.

[. . . ] TMS320C6455

www. ti. com SPRS276J MAY 2005 REVISED SEPTEMBER 2010

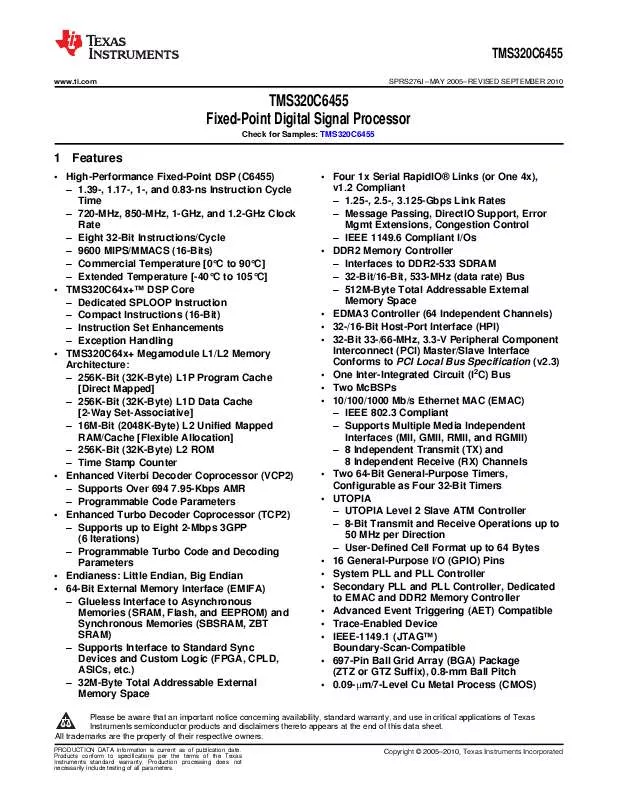

TMS320C6455 Fixed-Point Digital Signal Processor

Check for Samples: TMS320C6455

1 Features

12

· High-Performance Fixed-Point DSP (C6455) 1. 39-, 1. 17-, 1-, and 0. 83-ns Instruction Cycle Time 720-MHz, 850-MHz, 1-GHz, and 1. 2-GHz Clock Rate Eight 32-Bit Instructions/Cycle 9600 MIPS/MMACS (16-Bits) Commercial Temperature [0°C to 90°C] Extended Temperature [-40°C to 105°C] · TMS320C64x+TM DSP Core Dedicated SPLOOP Instruction Compact Instructions (16-Bit) Instruction Set Enhancements Exception Handling · TMS320C64x+ Megamodule L1/L2 Memory Architecture: 256K-Bit (32K-Byte) L1P Program Cache [Direct Mapped] 256K-Bit (32K-Byte) L1D Data Cache [2-Way Set-Associative] 16M-Bit (2048K-Byte) L2 Unified Mapped RAM/Cache [Flexible Allocation] 256K-Bit (32K-Byte) L2 ROM Time Stamp Counter · Enhanced Viterbi Decoder Coprocessor (VCP2) Supports Over 694 7. 95-Kbps AMR Programmable Code Parameters · Enhanced Turbo Decoder Coprocessor (TCP2) Supports up to Eight 2-Mbps 3GPP (6 Iterations) Programmable Turbo Code and Decoding Parameters · Endianess: Little Endian, Big Endian · 64-Bit External Memory Interface (EMIFA) Glueless Interface to Asynchronous Memories (SRAM, Flash, and EEPROM) and Synchronous Memories (SBSRAM, ZBT SRAM) Supports Interface to Standard Sync Devices and Custom Logic (FPGA, CPLD, ASICs, etc. ) 32M-Byte Total Addressable External Memory Space

1

· Four 1x Serial RapidIO® Links (or One 4x), v1. 2 Compliant 1. 25-, 2. 5-, 3. 125-Gbps Link Rates Message Passing, DirectIO Support, Error Mgmt Extensions, Congestion Control IEEE 1149. 6 Compliant I/Os · DDR2 Memory Controller Interfaces to DDR2-533 SDRAM 32-Bit/16-Bit, 533-MHz (data rate) Bus 512M-Byte Total Addressable External Memory Space · EDMA3 Controller (64 Independent Channels) · 32-/16-Bit Host-Port Interface (HPI) · 32-Bit 33-/66-MHz, 3. 3-V Peripheral Component Interconnect (PCI) Master/Slave Interface Conforms to PCI Local Bus Specification (v2. 3) · One Inter-Integrated Circuit (I2C) Bus · Two McBSPs · 10/100/1000 Mb/s Ethernet MAC (EMAC) IEEE 802. 3 Compliant Supports Multiple Media Independent Interfaces (MII, GMII, RMII, and RGMII) 8 Independent Transmit (TX) and 8 Independent Receive (RX) Channels · Two 64-Bit General-Purpose Timers, Configurable as Four 32-Bit Timers · UTOPIA UTOPIA Level 2 Slave ATM Controller 8-Bit Transmit and Receive Operations up to 50 MHz per Direction User-Defined Cell Format up to 64 Bytes · 16 General-Purpose I/O (GPIO) Pins · System PLL and PLL Controller · Secondary PLL and PLL Controller, Dedicated to EMAC and DDR2 Memory Controller · Advanced Event Triggering (AET) Compatible · Trace-Enabled Device · IEEE-1149. 1 (JTAGTM) Boundary-Scan-Compatible · 697-Pin Ball Grid Array (BGA) Package (ZTZ or GTZ Suffix), 0. 8-mm Ball Pitch · 0. 09-mm/7-Level Cu Metal Process (CMOS)

2

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

Copyright © 20052010, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

TMS320C6455

SPRS276J MAY 2005 REVISED SEPTEMBER 2010 www. ti. com

· 3. 3-/1. 8-/1. 5-/1. 25-/1. 2-V I/Os,

1. 25-/1. 2-V Internal

1. 1

ZTZ/GTZ BGA Package (Bottom View)

Figure 1-1 shows the TMS320C6455 device 697-pin ball grid array package (bottom view).

ZTZ/GTZ 697-PIN BALL GRID ARRAY (BGA) PACKAGE ( BOTTOM VIEW )

AJ AH AF AD AB Y V U T R P M K J H G F D C B A 1 2 3 4 5 6 7 8 9 11 13 15 17 19 21 23 25 27 29 10 12 14 16 18 20 22 24 26 28 E N L AG AE AC AA W

NOTE: The ZTZ mechanical package designator represents the version of the GTZ package with lead-free balls. [. . . ] Constant addressing mode is not supported by any other peripheral or internal memory in the C6455 DSP. Note that increment mode is supported by all C6455 peripherals, including VCP2 and TCP2. For more information on these two addressing modes, see the TMS320C645x DSP Enhanced DMA (EDMA3) Controller User's Guide (literature number SPRU966) . A DSP interrupt must be generated at the end of an HPI or PCI boot operation to begin execution of the loaded application. Since the DSP interrupt generated by the HPI and PCI is mapped to the EDMA event DSP_EVT (DMA channel 0), it will get recorded in bit 0 of the EDMA Event Register (ER). This event must be cleared by software before triggering transfers on DMA channel 0. The EDMA3 on the C6455 DSP supports active memory protection, but it does not support proxied memory protection.

7. 4. 2

EDMA3 Channel Synchronization Events

The EDMA3 supports up to 64 DMA channels that can be used to service system peripherals and to move data between system memories. DMA channels can be triggered by synchronization events generated by system peripherals. Table 7-3 lists the source of the synchronization event associated with each of the DMA channels. On the C6455 device, the association of each synchronization event and DMA channel is fixed and cannot be reprogrammed. For more detailed information on the EDMA3 module and how EDMA3 events are enabled, captured, processed, prioritized, linked, chained, and cleared, etc. , see the TMS320C645x DSP Enhanced DMA (EDMA3) Controller User's Guide (literature number SPRU966) . C6455 EDMA3 Channel Synchronization Events (1)

EDMA CHANNEL 0 (2) 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 (1) (2)

BINARY 000 0000 000 0001 000 0010 000 0011 000 0100 000 0101 000 0110 000 0111 000 1000 000 1001 000 1010 000 1011 000 1100 000 1101 000 1110 000 1111 001 0000 001 0001

EVENT NAME DSP_EVT TEVTLO0 TEVTHI0 XEVT0 REVT0 XEVT1 REVT1 TEVTLO1 TEVTHI1 HPI/PCI-to-DSP event

EVENT DESCRIPTION

Timer 0 lower counter event Timer 0 high counter event None None None None None None None None None McBSP0 transmit event McBSP0 receive event McBSP1 transmit event McBSP1 receive event Timer 1 lower counter event Timer 1 high counter event

In addition to the events shown in this table, each of the 64 channels can also be synchronized with the transfer completion or alternate transfer completion events. For more detailed information on EDMA event-transfer chaining, see the TMS320C645x DSP Enhanced DMA (EDMA3) Controller User's Guide (literature number SPRU966) . HPI boot and PCI boot are terminated using a DSP interrupt. The DSP interrupt is registered in bit 0 (channel 0) of the EDMA Event Register (ER). This event must be cleared by software before triggering transfers on DMA channel 0. C64x+ Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): TMS320C6455 107

Copyright © 20052010, Texas Instruments Incorporated

TMS320C6455

SPRS276J MAY 2005 REVISED SEPTEMBER 2010 www. ti. com

Table 7-3. C6455 EDMA3 Channel Synchronization Events (continued)

EDMA CHANNEL 18-19 20 21-27 28 29 30 31 32 33-39 40 41-43 44 45 46-47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 BINARY 001 0100 001 1100 001 1101 001 1110 001 1111 010 0000 010 1000 010 1100 010 1101 011 0000 011 0001 011 0010 011 0011 011 0100 011 0101 011 0110 011 0111 011 1000 011 1001 011 1010 011 1011 011 1100 011 1101 011 1110 011 1111 EVENT NAME INTDST1 VCP2REVT VCP2XEVT TCP2REVT TCP2XEVT UREVT UXEVT ICREVT ICXEVT GPINT0 GPINT1 GPINT2 GPINT3 GPINT4 GPINT5 GPINT6 GPINT7 GPINT8 GPINT9 GPINT10 GPINT11 GPINT12 GPINT13 GPINT14 GPINT15 None RapidIO Interrupt 1 None VCP2 receive event VCP2 transmit event TCP2 receive event TCP2 transmit event UTOPIA receive event None UTOPIA transmit event None I2C receive event I2C transmit event None GPIO event 0 GPIO event 1 GPIO event 2 GPIO event 3 GPIO event 4 GPIO event 5 GPIO event 6 GPIO event 7 GPIO event 8 GPIO event 9 GPIO event 10 GPIO event 11 GPIO event 12 GPIO event 13 GPIO event 14 GPIO event 15 EVENT DESCRIPTION

7. 4. 3

EDMA3 Peripheral Register Descriptions

Table 7-4. EDMA3 Channel Controller Registers

HEX ADDRESS RANGE 02A0 0000 02A0 0004 02A0 0008 - 02A0 00FC 02A0 0100 02A0 0104 02A0 0108 02A0 010C 02A0 0110 02A0 0114 02A0 0118 02A0 011C ACRONYM PID CCCFG DCHMAP0 DCHMAP1 DCHMAP2 DCHMAP3 DCHMAP4 DCHMAP5 DCHMAP6 DCHMAP7 Peripheral ID Register EDMA3CC Configuration Register Reserved DMA Channel 0 Mapping Register DMA Channel 1 Mapping Register DMA Channel 2 Mapping Register DMA Channel 3 Mapping Register DMA Channel 4 Mapping Register DMA Channel 5 Mapping Register DMA Channel 6 Mapping Register DMA Channel 7 Mapping Register REGISTER NAME

108

C64x+ Peripheral Information and Electrical Specifications Copyright © 20052010, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Link(s): TMS320C6455

TMS320C6455

www. ti. com SPRS276J MAY 2005 REVISED SEPTEMBER 2010

Table 7-4. EDMA3 Channel Controller Registers (continued)

HEX ADDRESS RANGE 02A0 0120 02A0 0124 02A0 0128 02A0 012C 02A0 0130 02A0 0134 02A0 0138 02A0 013C 02A0 0140 02A0 0144 02A0 0148 02A0 014C 02A0 0150 02A0 0154 02A0 0158 02A0 015C 02A0 0160 02A0 0164 02A0 0168 02A0 016C 02A0 0170 02A0 0174 02A0 0178 02A0 017C 02A0 0180 02A0 0184 02A0 0188 02A0 018C 02A0 0190 02A0 0194 02A0 0198 02A0 019C 02A0 01A0 02A0 01A4 02A0 01A8 02A0 01AC 02A0 01B0 02A0 01B4 02A0 01B8 02A0 01BC 02A0 01C0 02A0 01C4 02A0 01C8 02A0 01CC 02A0 01D0 02A0 01D4 02A0 01D8 ACRONYM DCHMAP8 DCHMAP9 DCHMAP10 DCHMAP11 DCHMAP12 DCHMAP13 DCHMAP14 DCHMAP15 DCHMAP16 DCHMAP17 DCHMAP18 DCHMAP19 DCHMAP20 DCHMAP21 DCHMAP22 DCHMAP23 DCHMAP24 DCHMAP25 DCHMAP26 DCHMAP27 DCHMAP28 DCHMAP29 DCHMAP30 DCHMAP31 DCHMAP32 DCHMAP33 DCHMAP34 DCHMAP35 DCHMAP36 DCHMAP37 DCHMAP38 DCHMAP39 DCHMAP40 DCHMAP41 DCHMAP42 DCHMAP43 DCHMAP44 DCHMAP45 DCHMAP46 DCHMAP47 DCHMAP48 DCHMAP49 DCHMAP50 DCHMAP51 DCHMAP52 DCHMAP53 DCHMAP54 REGISTER NAME DMA Channel 8 Mapping Register DMA Channel 9 Mapping Register DMA Channel 10 Mapping Register DMA Channel 11 Mapping Register DMA Channel 12 Mapping Register DMA Channel 13 Mapping Register DMA Channel 14 Mapping Register DMA Channel 15 Mapping Register DMA Channel 16 Mapping Register DMA Channel 17 Mapping Register DMA Channel 18 Mapping Register DMA Channel 19 Mapping Register DMA Channel 20 Mapping Register DMA Channel 21 Mapping Register DMA Channel 22 Mapping Register DMA Channel 23 Mapping Register DMA Channel 24 Mapping Register DMA Channel 25 Mapping Register DMA Channel 26 Mapping Register DMA Channel 27 Mapping Register DMA Channel 28 Mapping Register DMA Channel 29 Mapping Register DMA Channel 30 Mapping Register DMA Channel 31 Mapping Register DMA Channel 32 Mapping Register DMA Channel 33 Mapping Register DMA Channel 34 Mapping Register DMA Channel 35 Mapping Register DMA Channel 36 Mapping Register DMA Channel 37 Mapping Register DMA Channel 38 Mapping Register DMA Channel 39 Mapping Register DMA Channel 40 Mapping Register DMA Channel 41 Mapping Register DMA Channel 42 Mapping Register DMA Channel 43 Mapping Register DMA Channel 44 Mapping Register DMA Channel 45 Mapping Register DMA Channel 46 Mapping Register DMA Channel 47 Mapping Register DMA Channel 48 Mapping Register DMA Channel 49 Mapping Register DMA Channel 50 Mapping Register DMA Channel 51 Mapping Register DMA Channel 52 Mapping Register DMA Channel 53 Mapping Register DMA Channel 54 Mapping Register

Copyright © 20052010, Texas Instruments Incorporated

C64x+ Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): TMS320C6455

109

TMS320C6455

SPRS276J MAY 2005 REVISED SEPTEMBER 2010 www. ti. com

Table 7-4. EDMA3 Channel Controller Registers (continued)

HEX ADDRESS RANGE 02A0 01DC 02A0 01E0 02A0 01E4 02A0 01E8 02A0 01EC 02A0 01F0 02A0 01F4 02A0 01F8 02A0 01FC 02A0 0200 02A0 0204 02A0 0208 02A0 020C 02A0 0210 - 02A0 021C 02A0 0220 - 02A0 023C 02A0 0240 02A0 0244 02A0 0248 02A0 024C 02A0 0250 02A0 0254 02A0 0258 02A0 025C 02A0 0260 02A0 0264 - 02A0 0280 02A0 0284 02A0 0288 - 02A0 02FC 02A0 0300 02A0 0304 02A0 0308 02A0 030C 02A0 0310 02A0 0314 02A0 0318 02A0 031C 02A0 0320 02A0 0324 - 02A0 033C 02A0 0340 02A0 0344 02A0 0348 02A0 034C 02A0 0350 02A0 0354 02A0 0358 02A0 035C 02A0 0360 02A0 0364 ACRONYM DCHMAP55 DCHMAP56 DCHMAP57 DCHMAP58 DCHMAP59 DCHMAP60 DCHMAP61 DCHMAP62 DCHMAP63 QCHMAP0 QCHMAP1 QCHMAP2 QCHMAP3 DMAQNUM0 DMAQNUM1 DMAQNUM2 DMAQNUM3 DMAQNUM4 DMAQNUM5 DMAQNUM6 DMAQNUM7 QDMAQNUM QUEPRI EMR EMRH EMCR EMCRH QEMR QEMCR CCERR CCERRCLR EEVAL DRAE0 DRAEH0 DRAE1 DRAEH1 DRAE2 DRAEH2 DRAE3 DRAEH3 DRAE4 DRAEH4 REGISTER NAME DMA Channel 55 Mapping Register DMA Channel 56 Mapping Register DMA Channel 57 Mapping Register DMA Channel 58 Mapping Register DMA Channel 59 Mapping Register DMA Channel 60 Mapping Register DMA Channel 61 Mapping Register DMA Channel 62 Mapping Register DMA Channel 63 Mapping Register QDMA Channel 0 Mapping Register QDMA Channel 1 Mapping Register QDMA Channel 2 Mapping Register QDMA Channel 3 Mapping Register Reserved Reserved DMA Queue Number Register 0 DMA Queue Number Register 1 DMA Queue Number Register 2 DMA Queue Number Register 3 DMA Queue Number Register 4 DMA Queue Number Register 5 DMA Queue Number Register 6 DMA Queue Number Register 7 QDMA Queue Number Register Reserved Queue Priority Register Reserved Event Missed Register Event MissedRegister High Event Missed Clear Register Event Missed Clear Register High QDMA Event Missed Register QDMA Event Missed Clear Register EDMA3CC Error Register EDMA3CC Error Clear Register Error Evaluate Register Reserved DMA Region Access Enable Register for Region 0 DMA Region Access Enable Register High for Region 0 DMA Region Access Enable Register for Region 1 DMA Region Access Enable Register High for Region 1 DMA Region Access Enable Register for Region 2 DMA Region Access Enable Register High for Region 2 DMA Region Access Enable Register for Region 3 DMA Region Access Enable Register High for Region 3 DMA Region Access Enable Register for Region 4 DMA Region Access Enable Register High for Region 4

110

C64x+ Peripheral Information and Electrical Specifications Copyright © 20052010, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Link(s): TMS320C6455

TMS320C6455

www. ti. com SPRS276J MAY 2005 REVISED SEPTEMBER 2010

Table 7-4. EDMA3 Channel Controller Registers (continued)

HEX ADDRESS RANGE 02A0 0368 02A0 036C 02A0 0370 02A0 0374 02A0 0378 02A0 037C 02A0 0380 02A0 0384 02A0 0388 02A0 038C 02A0 0390 - 02A0 039C 02A0 0400 02A0 0404 02A0 0408 02A0 040C 02A0 0410 02A0 0414 02A0 0418 02A0 041C 02A0 0420 02A0 0424 02A0 0428 02A0 042C 02A0 0430 02A0 0434 02A0 0438 02A0 043C 02A0 0440 02A0 0444 02A0 0448 02A0 044C 02A0 0450 02A0 0454 02A0 0458 02A0 045C 02A0 0460 02A0 0464 02A0 0468 02A0 046C 02A0 0470 02A0 0474 02A0 0478 02A0 047C 02A0 0480 02A0 0484 02A0 0488 02A0 048C ACRONYM DRAE5 DRAEH5 DRAE6 DRAEH6 DRAE7 DRAEH7 QRAE0 QRAE1 QRAE2 QRAE3 Q0E0 Q0E1 Q0E2 Q0E3 Q0E4 Q0E5 Q0E6 Q0E7 Q0E8 Q0E9 Q0E10 Q0E11 Q0E12 Q0E13 Q0E14 Q0E15 Q1E0 Q1E1 Q1E2 Q1E3 Q1E4 Q1E5 Q1E6 Q1E7 Q1E8 Q1E9 Q1E10 Q1E11 Q1E12 Q1E13 Q1E14 Q1E15 Q2E0 Q2E1 Q2E2 Q2E3 REGISTER NAME DMA Region Access Enable Register for Region 5 DMA Region Access Enable Register High for Region 5 DMA Region Access Enable Register for Region 6 DMA Region Access Enable Register High for Region 6 DMA Region Access Enable Register for Region 7 DMA Region Access Enable Register High for Region 7 QDMA Region Access Enable Register for Region 0 QDMA Region Access Enable Register for Region 1 QDMA Region Access Enable Register for Region 2 QDMA Region Access Enable Register for Region 3 Reserved Event Queue 0 Entry Register 0 Event Queue 0 Entry Register 1 Event Queue 0 Entry Register 2 Event Queue 0 Entry Register 3 Event Queue 0 Entry Register 4 Event Queue 0 Entry Register 5 Event Queue 0 Entry Register 6 Event Queue 0 Entry Register 7 Event Queue 0 Entry Register 8 Event Queue 0 Entry Register 9 Event Queue 0 Entry Register 10 Event Queue 0 Entry Register 11 Event Queue 0 Entry Register 12 Event Queue 0 Entry Register 13 Event Queue 0 Entry Register 14 Event Queue 0 Entry Register 15 Event Queue 1 Entry Register 0 Event Queue 1 Entry Register 1 Event Queue 1 Entry Register 2 Event Queue 1 Entry Register 3 Event Queue 1 Entry Register 4 Event Queue 1 Entry Register 5 Event Queue 1 Entry Register 6 Event Queue 1 Entry Register 7 Event Queue 1 Entry Register 8 Event Queue 1 Entry Register 9 Event Queue 1 Entry Register 10 Event Queue 1 Entry Register 11 Event Queue 1 Entry Register 12 Event Queue 1 Entry Register 13 Event Queue 1 Entry Register 14 Event Queue 1 Entry Register 15 Event Queue 2 Entry Register 0 Event Queue 2 Entry Register 1 Event Queue 2 Entry Register 2 Event Queue 2 Entry Register 3

Copyright © 20052010, Texas Instruments Incorporated

C64x+ Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): TMS320C6455

111

TMS320C6455

SPRS276J MAY 2005 REVISED SEPTEMBER 2010 www. ti. com

Table 7-4. [. . . ] All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. [. . . ]

DISCLAIMER TO DOWNLOAD THE USER GUIDE TEXAS INSTRUMENTS TMS320C6455 Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets...manual TEXAS INSTRUMENTS TMS320C6455