User manual TEXAS INSTRUMENTS TMS320C6474 DATA MANUAL REV F

Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets... DON'T FORGET : ALWAYS READ THE USER GUIDE BEFORE BUYING !!!

If this document matches the user guide, instructions manual or user manual, feature sets, schematics you are looking for, download it now. Lastmanuals provides you a fast and easy access to the user manual TEXAS INSTRUMENTS TMS320C6474. We hope that this TEXAS INSTRUMENTS TMS320C6474 user guide will be useful to you.

Lastmanuals help download the user guide TEXAS INSTRUMENTS TMS320C6474.

Manual abstract: user guide TEXAS INSTRUMENTS TMS320C6474DATA MANUAL REV F

Detailed instructions for use are in the User's Guide.

[. . . ] TMS320C6474

www. ti. com SPRS552F OCTOBER 2008 REVISED JULY 2010

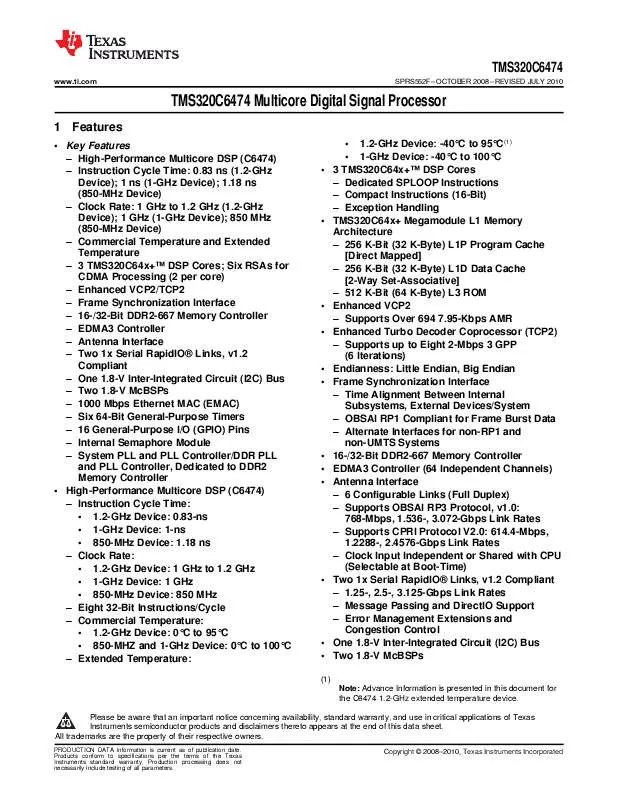

TMS320C6474 Multicore Digital Signal Processor

1 Features

12

· Key Features High-Performance Multicore DSP (C6474) Instruction Cycle Time: 0. 83 ns (1. 2-GHz Device); 1 ns (1-GHz Device); 1. 18 ns (850-MHz Device) Clock Rate: 1 GHz to 1. 2 GHz (1. 2-GHz Device); 1 GHz (1-GHz Device); 850 MHz (850-MHz Device) Commercial Temperature and Extended Temperature 3 TMS320C64x+TM DSP Cores; Six RSAs for CDMA Processing (2 per core) Enhanced VCP2/TCP2 Frame Synchronization Interface 16-/32-Bit DDR2-667 Memory Controller EDMA3 Controller Antenna Interface Two 1x Serial RapidIO® Links, v1. 2 Compliant One 1. 8-V Inter-Integrated Circuit (I2C) Bus Two 1. 8-V McBSPs 1000 Mbps Ethernet MAC (EMAC) Six 64-Bit General-Purpose Timers 16 General-Purpose I/O (GPIO) Pins Internal Semaphore Module System PLL and PLL Controller/DDR PLL and PLL Controller, Dedicated to DDR2 Memory Controller · High-Performance Multicore DSP (C6474) Instruction Cycle Time: · 1. 2-GHz Device: 0. 83-ns · 1-GHz Device: 1-ns · 850-MHz Device: 1. 18 ns Clock Rate: · 1. 2-GHz Device: 1 GHz to 1. 2 GHz · 1-GHz Device: 1 GHz · 850-MHz Device: 850 MHz Eight 32-Bit Instructions/Cycle Commercial Temperature: · 1. 2-GHz Device: 0°C to 95°C · 850-MHZ and 1-GHz Device: 0°C to 100°C Extended Temperature:

·

·

· ·

· ·

· · ·

·

· ·

(1)

· 1. 2-GHz Device: -40°C to 95°C (1) · 1-GHz Device: -40°C to 100°C 3 TMS320C64x+TM DSP Cores Dedicated SPLOOP Instructions Compact Instructions (16-Bit) Exception Handling TMS320C64x+ Megamodule L1 Memory Architecture 256 K-Bit (32 K-Byte) L1P Program Cache [Direct Mapped] 256 K-Bit (32 K-Byte) L1D Data Cache [2-Way Set-Associative] 512 K-Bit (64 K-Byte) L3 ROM Enhanced VCP2 Supports Over 694 7. 95-Kbps AMR Enhanced Turbo Decoder Coprocessor (TCP2) Supports up to Eight 2-Mbps 3 GPP (6 Iterations) Endianness: Little Endian, Big Endian Frame Synchronization Interface Time Alignment Between Internal Subsystems, External Devices/System OBSAI RP1 Compliant for Frame Burst Data Alternate Interfaces for non-RP1 and non-UMTS Systems 16-/32-Bit DDR2-667 Memory Controller EDMA3 Controller (64 Independent Channels) Antenna Interface 6 Configurable Links (Full Duplex) Supports OBSAI RP3 Protocol, v1. 0: 768-Mbps, 1. 536-, 3. 072-Gbps Link Rates Supports CPRI Protocol V2. 0: 614. 4-Mbps, 1. 2288-, 2. 4576-Gbps Link Rates Clock Input Independent or Shared with CPU (Selectable at Boot-Time) Two 1x Serial RapidIO® Links, v1. 2 Compliant 1. 25-, 2. 5-, 3. 125-Gbps Link Rates Message Passing and DirectIO Support Error Management Extensions and Congestion Control One 1. 8-V Inter-Integrated Circuit (I2C) Bus Two 1. 8-V McBSPs

Note: Advance Information is presented in this document for the C6474 1. 2-GHz extended temperature device.

1

2

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

Copyright © 20082010, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

TMS320C6474

SPRS552F OCTOBER 2008 REVISED JULY 2010 www. ti. com

· 1000 Mbps Ethernet MAC (EMAC) IEEE 802. 3 Compliant Supports SGMII, v1. 8 Compliant 8 Independent Transmit (TX) and 8 Independent Receive (RX) Channels · Six 64-Bit General-Purpose Timers Configurable up to Twelve 32-Bit Timers Configurable in a Watchdog Timer mode · 16 General-Purpose I/O (GPIO) Pins · Internal Semaphore Module Software Method to Control Access to Shared Resources

32 General Purpose Semaphore Resources · System PLL and PLL Controller · DDR PLL and PLL Controller, Dedicated to DDR2 Memory Controller · IEEE-1149. 1 and IEEE-1149. 6 (JTAGTM) Boundary-Scan-Compatible · 561-Pin Ball Grid Array (BGA) Packages (CUN, GUN, or ZUN Suffix), 0. 8-mm Ball Pitch · 0. 065-mm/7-Level Cu Metal Process (CMOS) · SmartReflexTM Class 0 - 0. 9-V to 1. 2-V Adaptive Core Voltage · 1. 8-V, 1. 1-V I/Os

1. 1

CUN/GUN/ZUN BGA Package (Bottom View)

The devices are designed for a package temperature range of 0°C to 100°C (commercial temperature range; 1-GHz device), -40°C to 100°C (extended temperature range; 1-GHz device), 0°C to 95°C (commercial temperature range; 850-MHz and 1. 2-GHz device), and -40°C to 95°C (extended temperature range; 1. 2-GHz device). [. . . ] C64x+ Megamodule Chip Interrupt Controller Event List CIC[2:0] (continued)

EVENT CHANNEL 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55-57 58 59-63 (1) EVENT IREVT IXEVT FSEVT18 FSEVT19 FSEVT20 FSEVT21 FSEVT22 FSEVT23 FSEVT24 FSEVT25 FSEVT26 FSEVT27 FSEVT28 FSEVT29 VCPREVT VCPXEVT TCPREVT TCPXEVT TPCC_ERRINT TPCC_MPINT TPTC_ERRINT0 TPTC_ERRINT1 TPTC_ERRINT2 TPTC_ERRINT3 TPTC_ERRINT4 TPTC_ERRINT5 TPCC_AETEVT AIF_EVT2 AIF_EVT3 AIF_PSEVT0 AIF_PSEVT1 AIF_PSEVT2 AIF_PSEVT3 AIF_PSEVT4 AIF_PSEVT5 AIF_PSEVT6 AIF_BUFEVT Unused SEMERRn Unused

(1)

EVENT DESCRIPTION I2C Receive EDMA Event I2C Transmit EDMA Event FSYNC Event 18 FSYNC Event 19 FSYNC Event 20 FSYNC Event 21 FSYNC Event 22 FSYNC Event 23 FSYNC Event 24 FSYNC Event 25 FSYNC Event 26 FSYNC Event 27 FSYNC Event 28 FSYNC Event 28 VCP Receive Event VCP Transmit Event TCP Receive Event TCP Transmit Event TPCC Error Interrupt TPCC Memory Protection Interrupt TPTC0 Error Interrupt TPTC1 Error Interrupt TPTC2 Error Interrupt TPTC3 Error Interrupt TPTC4 Error Interrupt TPTC5 Error Interrupt TPCC AET Event AIF CPU Interrupt 2 AIF CPU Interrupt 2 Packet Switched Transfer Event 0 Packet Switched Transfer Event 1 Packet Switched Transfer Event 2 Packet Switched Transfer Event 3 Packet Switched Transfer Event 4 Packet Switched Transfer Event 5 Packet Switched Transfer Event 6 AIF Capture Buffer Event. Reserved Semaphore Error Event for C64x+ Megamodulen Reserved

C64x+ Megamodule Core 0, C64x+ Megamodule Core 1, and C64x+ Megamodule Core 2 receive SEMERR0, SEMERR1, and SEMERR2, respectively.

Another system event selector is present to route events to the TPCC. Most system events routed through the event controller to the TPCC are CPU events that do not normally require DMA servicing, but may be used to trigger a statistics capture. Several events are routed through the event controller that may be used to trigger a DMA transaction in normal operation, but the programmer must make a resource tradeoff to use these events. Table 7-16 lists all of the events routed through the TPCCs system event controller.

108 Peripheral Information and Electrical Specifications Copyright © 20082010, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Link(s) :TMS320C6474

TMS320C6474

www. ti. com SPRS552F OCTOBER 2008 REVISED JULY 2010

Table 7-16. TPCC Interrupt Controller Event List (CIC3)

EVENT CHANNEL 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40-42 43 44 45 46 47 48 EVENT EVT0 EVT1 FSEVT0 FSEVT1 FSEVT2 FSEVT3 FSEVT14 FSEVT15 FSEVT16 FSEVT17 FSEVT18 FSEVT19 FSEVT20 FSEVT21 FSEVT22 FSEVT23 FSEVT24 FSEVT25 FSEVT26 FSEVT27 FSEVT28 RIOINT0 RIOINT1 RIOINT2 RIOINT3 RIOINT4 RIOINT5 RIOINT7 MACINT[0] MACRXINT[0] MACTXINT[0] MACINT[1] MACRXINT[1] MACTXINT[1] MACINT[2] MACRXINT[2] MACTXINT[2] SEMERR0 SEMERR1 SEMERR2 Unused TINT3L TINT3H TINT4L TINT4H TINT5L TINT5H EVENT DESCRIPTION Output of Event Controller 0 for Events [31:2] Output of Event Controller 1 for Events [63:32] Frame Synchronization Event 0 Frame Synchronization Event 1 Frame Synchronization Event 2 Frame Synchronization Event 3 Frame Synchronization Event 14 Frame Synchronization Event 15 Frame Synchronization Event 16 Frame Synchronization Event 17 Frame Synchronization Event 18 Frame Synchronization Event 19 Frame Synchronization Event 20 Frame Synchronization Event 21 Frame Synchronization Event 22 Frame Synchronization Event 23 Frame Synchronization Event 24 Frame Synchronization Event 25 Frame Synchronization Event 26 Frame Synchronization Event 27 Frame Synchronization Event 28 RapidIO Interrupt 0 RapidIO Interrupt 1 RapidIO Interrupt 2 RapidIO Interrupt 3 RapidIO Interrupt 4 RapidIO Interrupt 5 RapidIO Interrupt 7 Ethernet EMAC Interrupt Ethernet EMAC Interrupt Ethernet EMAC Interrupt Ethernet EMAC Interrupt Ethernet EMAC Interrupt Ethernet EMAC Interrupt Ethernet EMAC Interrupt Ethernet EMAC Interrupt Ethernet EMAC Interrupt Semaphore Error Interrupt Semaphore Error Interrupt Semaphore Error Interrupt Reserved Timer Interrupt Low Timer Interrupt High Timer Interrupt Low Timer Interrupt High Timer Interrupt Low Timer Interrupt High Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s) :TMS320C6474 109

Copyright © 20082010, Texas Instruments Incorporated

TMS320C6474

SPRS552F OCTOBER 2008 REVISED JULY 2010 www. ti. com

Table 7-16. TPCC Interrupt Controller Event List (CIC3) (continued)

EVENT CHANNEL 49 50 51-52 53 54 55 56 57 58 59 60 61 62 63 EVENT AIF_BUFEVT FSEVT29 Unused GPINT0 GPINT1 GPINT2 GPINT3 GPINT4 CIC0_EVT14 CIC0_EVT15 CIC1_EVT14 CIC1_EVT15 CIC2_EVT14 CIC2_EVT15 AIF Capture Buffer Event Frame Synchronization Event 29 Reserved GPIO Event GPIO Event GPIO Event GPIO Event GPIO Event CIC_EVT_o[14] from Chip Interrupt Controller[0] CIC_EVT_o[15] from Chip Interrupt Controller[0] CIC_EVT_o[14] from Chip Interrupt Controller[1] CIC_EVT_o[15] from Chip Interrupt Controller[1] CIC_EVT_o[14] from Chip Interrupt Controller[2] CIC_EVT_o[15] from Chip Interrupt Controller[2] EVENT DESCRIPTION

110

Peripheral Information and Electrical Specifications Copyright © 20082010, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Link(s) :TMS320C6474

TMS320C6474

www. ti. com SPRS552F OCTOBER 2008 REVISED JULY 2010

7. 6. 3

External Interrupts Electrical Data/Timing

Table 7-17. Timing Requirements for External Interrupts (1)

(see Figure 7-5)

NO. 1 2 (1) tw(NMIL) tw(NMIH) PARAMETERS Width of the NMI interrupt pulse low Width of the NMI interrupt pulse high MIN 6P 6P MAX UNIT ns ns

P = 1/CPU clock frequency, in ns. For example, when running parts at 1000 MHz, use P = 1 ns.

2

1 NMI

Figure 7-5. NMI Interrupt Timing

Copyright © 20082010, Texas Instruments Incorporated

Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s) :TMS320C6474

111

TMS320C6474

SPRS552F OCTOBER 2008 REVISED JULY 2010 www. ti. com

7. 7

Reset Controller

The reset controller detects the different type of resets supported on the device and manages the distribution of those resets throughout the device. The C6474 device has several types of resets: power-on reset, warm reset, system reset, and CPU reset. Table 7-18 explains further the types of reset, the reset initiator, and the effects of each reset on the chip. Reset Types

TYPE INITIATOR POR pin XWRST pin Emulator Serial RapidIO Watchdog Timer EFFECT(S) Resets the entire chip including the test and emulation logic. Resets everything except for the test and emulation logic PLL2, AIF, and FSYNC. Emulation stays alive during warm reset. A system reset maintains memory contents and does not reset the test and emulation circuitry. The device configuration pins are also not re-latched and the state of the peripherals (enabled/disabled) are also not affected. CPU local reset.

Power-on Reset Warm Reset System Reset

CPU Local Reset

7. 7. 1

Power-on Reset (POR Pin)

Power-on Reset is a special reset needed when powering on the DSP. The device is globally reset through the assertion of the active-low Power-on Reset (POR) input. The power-on reset is intended to be asserted to the device while the system power supplies are ramped. For power-on reset, the main PLL Controller comes up in bypass and the PLL is not enabled. [. . . ] All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. [. . . ]

DISCLAIMER TO DOWNLOAD THE USER GUIDE TEXAS INSTRUMENTS TMS320C6474 Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets...manual TEXAS INSTRUMENTS TMS320C6474