Detailed instructions for use are in the User's Guide.

[. . . ] TMS320C6745/6747

www. ti. com SPRS377D SEPTEMBER 2008 REVISED AUGUST 2010

TMS320C6745/6747 Fixed/Floating-point Digital Signal Processor

Check for Samples: TMS320C6745/6747

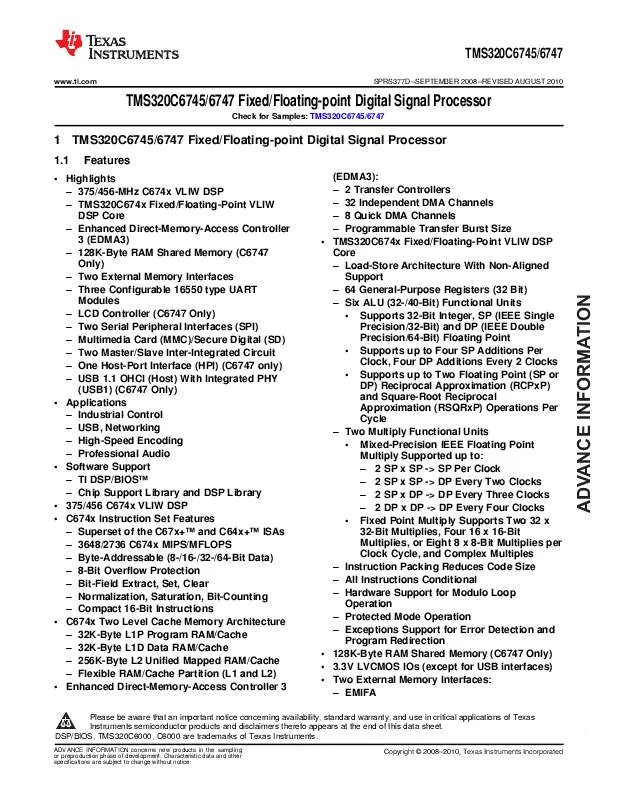

1 TMS320C6745/6747 Fixed/Floating-point Digital Signal Processor

1. 1

12

Features

(EDMA3): 2 Transfer Controllers 32 Independent DMA Channels 8 Quick DMA Channels Programmable Transfer Burst Size TMS320C674x Fixed/Floating-Point VLIW DSP Core Load-Store Architecture With Non-Aligned Support 64 General-Purpose Registers (32 Bit) Six ALU (32-/40-Bit) Functional Units · Supports 32-Bit Integer, SP (IEEE Single Precision/32-Bit) and DP (IEEE Double Precision/64-Bit) Floating Point · Supports up to Four SP Additions Per Clock, Four DP Additions Every 2 Clocks · Supports up to Two Floating Point (SP or DP) Reciprocal Approximation (RCPxP) and Square-Root Reciprocal Approximation (RSQRxP) Operations Per Cycle Two Multiply Functional Units · Mixed-Precision IEEE Floating Point Multiply Supported up to: 2 SP x SP -> SP Per Clock 2 SP x SP -> DP Every Two Clocks 2 SP x DP -> DP Every Three Clocks 2 DP x DP -> DP Every Four Clocks · Fixed Point Multiply Supports Two 32 x 32-Bit Multiplies, Four 16 x 16-Bit Multiplies, or Eight 8 x 8-Bit Multiplies per Clock Cycle, and Complex Multiples Instruction Packing Reduces Code Size All Instructions Conditional Hardware Support for Modulo Loop Operation Protected Mode Operation Exceptions Support for Error Detection and Program Redirection 128K-Byte RAM Shared Memory (C6747 Only) 3. 3V LVCMOS IOs (except for USB interfaces) Two External Memory Interfaces: EMIFA

· Highlights 375/456-MHz C674x VLIW DSP TMS320C674x Fixed/Floating-Point VLIW DSP Core Enhanced Direct-Memory-Access Controller 3 (EDMA3) 128K-Byte RAM Shared Memory (C6747 Only) Two External Memory Interfaces Three Configurable 16550 type UART Modules LCD Controller (C6747 Only) Two Serial Peripheral Interfaces (SPI) Multimedia Card (MMC)/Secure Digital (SD) Two Master/Slave Inter-Integrated Circuit One Host-Port Interface (HPI) (C6747 only) USB 1. 1 OHCI (Host) With Integrated PHY (USB1) (C6747 Only) · Applications Industrial Control USB, Networking High-Speed Encoding Professional Audio · Software Support TI DSP/BIOSTM Chip Support Library and DSP Library · 375/456 C674x VLIW DSP · C674x Instruction Set Features Superset of the C67x+TM and C64x+TM ISAs 3648/2736 C674x MIPS/MFLOPS Byte-Addressable (8-/16-/32-/64-Bit Data) 8-Bit Overflow Protection Bit-Field Extract, Set, Clear Normalization, Saturation, Bit-Counting Compact 16-Bit Instructions · C674x Two Level Cache Memory Architecture 32K-Byte L1P Program RAM/Cache 32K-Byte L1D Data RAM/Cache 256K-Byte L2 Unified Mapped RAM/Cache Flexible RAM/Cache Partition (L1 and L2) · Enhanced Direct-Memory-Access Controller 3

1

·

· · ·

2

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. DSP/BIOS, TMS320C6000, C6000 are trademarks of Texas Instruments.

Copyright © 20082010, Texas Instruments Incorporated

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

ADVANCE INFORMATION

TMS320C6745/6747

SPRS377D SEPTEMBER 2008 REVISED AUGUST 2010 www. ti. com

·

· ·

· · ·

·

· ·

NOR (8-/16-Bit-Wide Data) NAND (8-/16-Bit-Wide Data) 16-Bit SDRAM With 128MB Address Space (C6747 Only) EMIFB · 32-Bit or 16-Bit SDRAM With 256MB Address Space (C6747) · 16-Bit SDRAM With 256MB Address Space (C6745) Three Configurable 16550 type UART Modules: UART0 With Modem Control Signals Autoflow control signals (CTS, RTS) on UART0 only 16-byte FIFO 16x or 13x Oversampling Option LCD Controller (C6747 Only) Two Serial Peripheral Interfaces (SPI) Each With One Chip-Select Multimedia Card (MMC)/Secure Digital (SD) Card Interface with Secure Data I/O (SDIO) Two Master/Slave Inter-Integrated Circuit (I2C BusTM) One Host-Port Interface (HPI) With 16-Bit-Wide Muxed Address/Data Bus For High Bandwidth (C6747 only) Programmable Real-Time Unit Subsystem (PRUSS) Two Independent Programmable Realtime Unit (PRU) Cores · 32-Bit Load/Store RISC architecture · 4K Byte instruction RAM per core · 512 Bytes data RAM per core · PRU Subsystem (PRUSS) can be disabled via software to save power Standard power management mechanism · Clock gating · Entire subsystem under a single PSC clock gating domain Dedicated interrupt controller Dedicated switched central resource USB 1. 1 OHCI (Host) With Integrated PHY (USB1) (C6747 Only) USB 2. 0 OTG Port With Integrated PHY (USB0) USB 2. 0 High-/Full-Speed Client (C6747) USB 2. 0 Full-Speed Client (C6745) USB 2. 0 High-/Full-/Low-Speed Host (C6747) USB 2. 0 Full-/Low-Speed Host (C6745) High-speed Functionality Available on C6747 Device Only

· · ·

·

·

· · ·

·

·

· ·

·

· ·

End Point 0 (Control) End Points 1, 2, 3, 4 (Control, Bulk, Interrupt or ISOC) Rx and Tx Three Multichannel Audio Serial Ports: C6747 supports 3 McASPs C6745 supports 2 McASPs Six Clock Zones and 28 Serial Data Pins Supports TDM, I2S, and Similar Formats DIT-Capable (McASP2) FIFO buffers for Transmit and Receive 10/100 Mb/s Ethernet MAC (EMAC): IEEE 802. 3 Compliant (3. 3-V I/O Only) RMII Media Independent Interface Management Data I/O (MDIO) Module Real-Time Clock With 32 KHz Oscillator and Separate Power Rail (C6747 Only) One 64-Bit General-Purpose Timer (Configurable as Two 32-Bit Timers) One 64-bit General-Purpose/Watchdog Timer (Configurable as Two 32-bit General-Purpose Timers) Three Enhanced Pulse Width Modulators (eHRPWM): Dedicated 16-Bit Time-Base Counter With Period And Frequency Control 6 Single Edge, 6 Dual Edge Symmetric or 3 Dual Edge Asymmetric Outputs Dead-Band Generation PWM Chopping by High-Frequency Carrier Trip Zone Input Three 32-Bit Enhanced Capture Modules (eCAP): Configurable as 3 Capture Inputs or 3 Auxiliary Pulse Width Modulator (APWM) outputs Single Shot Capture of up to Four Event Time-Stamps Two 32-Bit Enhanced Quadrature Encoder Pulse Modules (eQEP) C6747 Device: 256-Ball Pb-Free Plastic Ball Grid Array (PBGA) [ZKB Suffix], 1. 0-mm Ball Pitch C6745 Device 176-pin PowerPADTM Plastic Quad Flat Pack [PTP suffix], 0. 5-mm Pin Pitch Commercial, Industrial, Extended, or Automotive Temperature Community Resources TI E2E Community TI Embedded Processors Wiki

ADVANCE INFORMATION

2

TMS320C6745/6747 Fixed/Floating-point Digital Signal Processor Copyright © 20082010, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Link(s): TMS320C6745/6747

TMS320C6745/6747

www. ti. com SPRS377D SEPTEMBER 2008 REVISED AUGUST 2010

1. 2

Trademarks

DSP/BIOS, TMS320C6000, C6000, TMS320, TMS320C62x, and TMS320C67x are trademarks of Texas Instruments. All trademarks are the property of their respective owners.

Copyright © 20082010, Texas Instruments Incorporated

TMS320C6745/6747 Fixed/Floating-point Digital Signal Processor Submit Documentation Feedback Product Folder Link(s): TMS320C6745/6747

3

ADVANCE INFORMATION

TMS320C6745/6747

SPRS377D SEPTEMBER 2008 REVISED AUGUST 2010 www. ti. com

1. 3

Description

The C6745/6747 is a low-power digital signal processor based on C674x DSP core. [. . . ] This allows a single handshake line to be shared by multiple slaves on the same SPI bus. In master mode, the SPIx_ENA pin is an optional input and the master can be configured to delay the start of the next transfer until the slave asserts SPIx_ENA. The addition of this handshake signal simplifies SPI communications and, on average, increases SPI bus throughput since the master does not need to delay each transfer long enough to allow for the worst-case latency of the slave device. Instead, each transfer can begin as soon as both the master and slave have actually serviced the previous SPI transfer. Although the SPI module supports two interrupt outputs, SPIx_INT1 is the only interrupt connected on this device.

Copyright © 20082010, Texas Instruments Incorporated

Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): TMS320C6745/6747

125

ADVANCE INFORMATION

Figure 6-34. Block Diagram of SPI Module

TMS320C6745/6747

SPRS377D SEPTEMBER 2008 REVISED AUGUST 2010 www. ti. com

Optional - Slave Chip Select SPIx_SCS Optional Enable (Ready) SPIx_ENA SPIx_ENA SPIx_SCS

SPIx_CLK

SPIx_CLK

SPIx_SOMI

SPIx_SOMI

SPIx_SIMO

SPIx_SIMO

ADVANCE INFORMATION

126

MASTER SPI

SLAVE SPI

Figure 6-35. Illustration of SPI Master-to-SPI Slave Connection

Peripheral Information and Electrical Specifications Copyright © 20082010, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Link(s): TMS320C6745/6747

TMS320C6745/6747

www. ti. com SPRS377D SEPTEMBER 2008 REVISED AUGUST 2010

6. 18. 1 SPI Peripheral Registers Description(s)

Table 6-53 is a list of the SPI registers. SPIx Configuration Registers

SPI0 BYTE ADDRESS 0x01C4 1000 0x01C4 1004 0x01C4 1008 0x01C4 100C 0x01C4 1010 0x01C4 1014 0x01C4 1018 0x01C4 101C 0x01C4 1020 0x01C4 1024 0x01C4 1028 0x01C4 102C 0x01C4 1030 0x01C4 1034 0x01C4 1038 0x01C4 103C 0x01C4 1040 0x01C4 1044 0x01C4 1048 0x01C4 104C 0x01C4 1050 0x01C4 1054 0x01C4 1058 0x01C4 105C 0x01C4 1060 0x01C4 1064 SPI1 BYTE ADDRESS 0x01E1 2000 0x01E1 2004 0x01E1 2008 0x01E1 200C 0x01E1 2010 0x01E1 2014 0x01E1 2018 0x01E1 201C 0x01E1 2020 0x01E1 2024 0x01E1 2028 0x01E1 202C 0x01E1 2030 0x01E1 2034 0x01E1 2038 0x01E1 203C 0x01E1 2040 0x01E1 2044 0x01E1 2048 0x01E1 204C 0x01E1 2050 0x01E1 2054 0x01E1 2058 0x01E1 205C 0x01E1 2060 0x01E1 2064 ACRONYM SPIGCR0 SPIGCR1 SPIINT0 SPILVL SPIFLG SPIPC0 SPIPC1 SPIPC2 SPIPC3 SPIPC4 SPIPC5 Reserved Reserved Reserved SPIDAT0 SPIDAT1 SPIBUF SPIEMU SPIDELAY SPIDEF SPIFMT0 SPIFMT1 SPIFMT2 SPIFMT3 Reserved INTVEC1 REGISTER DESCRIPTION Global Control Register 0 Global Control Register 1 Interrupt Register Interrupt Level Register Flag Register Pin Control Register 0 (Pin Function) Pin Control Register 1 (Pin Direction) Pin Control Register 2 (Pin Data In) Pin Control Register 3 (Pin Data Out) Pin Control Register 4 (Pin Data Set) Reserved - Do not write to this register Reserved - Do not write to this register Reserved - Do not write to this register Shift Register 0 (without format select) Shift Register 1 (with format select) Buffer Register Emulation Register Delay Register Default Chip Select Register Format Register 0 Format Register 1 Format Register 2 Format Register 3 Reserved - Do not write to this register Interrupt Vector for SPI INT1 Pin Control Register 5 (Pin Data Clear)

Copyright © 20082010, Texas Instruments Incorporated

Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): TMS320C6745/6747

127

ADVANCE INFORMATION

TMS320C6745/6747

SPRS377D SEPTEMBER 2008 REVISED AUGUST 2010 www. ti. com

6. 18. 2 SPI Electrical Data/Timing

6. 18. 2. 1 Serial Peripheral Interface (SPI) Timing Table 6-54 through Table 6-69 assume testing over recommended operating conditions (see Figure 6-36 through Figure 6-39). General Timing Requirements for SPI0 Master Modes (1)

No. 1 2 3 tc(SPC)M tw(SPCH)M tw(SPCL)M PARAMATER Cycle Time, SPI0_CLK, All Master Modes Pulse Width High, SPI0_CLK, All Master Modes Pulse Width Low, SPI0_CLK, All Master Modes Polarity = 0, Phase = 0, to SPI0_CLK rising Delay, initial data bit valid on SPI0_SIMO after initial edge on SPI0_CLK (2) Polarity = 0, Phase = 1, to SPI0_CLK rising Polarity = 1, Phase = 0, to SPI0_CLK falling Polarity = 1, Phase = 1, to SPI0_CLK falling Polarity = 0, Phase = 0, from SPI0_CLK rising Delay, subsequent bits valid on SPI0_SIMO after transmit edge of SPI0_CLK Polarity = 0, Phase = 1, from SPI0_CLK falling Polarity = 1, Phase = 0, from SPI0_CLK falling Polarity = 1, Phase = 1, from SPI0_CLK rising Polarity = 0, Phase = 0, from SPI0_CLK falling Output hold time, SPI0_SIMO valid after receive edge of SPI0_CLK Polarity = 0, Phase = 1, from SPI0_CLK rising Polarity = 1, Phase = 0, from SPI0_CLK rising Polarity = 1, Phase = 1, from SPI0_CLK falling Polarity = 0, Phase = 0, to SPI0_CLK falling Input Setup Time, SPI0_SOMI valid before receive edge of SPI0_CLK Polarity = 0, Phase = 1, to SPI0_CLK rising Polarity = 1, Phase = 0, to SPI0_CLK rising Polarity = 1, Phase = 1, to SPI0_CLK falling Polarity = 0, Phase = 0, from SPI0_CLK falling Input Hold Time, SPI0_SOMI valid after receive edge of SPI0_CLK Polarity = 0, Phase = 1, from SPI0_CLK rising Polarity = 1, Phase = 0, from SPI0_CLK rising Polarity = 1, Phase = 1, from SPI0_CLK falling (1) (2) 0. 5tc(SPC)M -3 0. 5tc(SPC)M -3 ns 0. 5tc(SPC)M -3 0. 5tc(SPC)M -3 0 0 ns 0 0 5 5 ns 5 5 MIN greater of 3P or 20 ns 0. 5tc(SPC)M - 1 0. 5tc(SPC)M - 1 5 - 0. 5tc(SPC)M + 5 ns 5 - 0. 5tc(SPC)M + 5 5 5 ns 5 5 MAX 256P UNIT ns ns ns

4

td(SIMO_SPC)M

ADVANCE INFORMATION

5

td(SPC_SIMO)M

6

toh(SPC_SIMO)M

7

tsu(SOMI_SPC)M

8

tih(SPC_SOMI)M

P = SYSCLK2 period First bit may be MSB or LSB depending upon SPI configuration. MO(0) refers to first bit and MO(n) refers to last bit output on SPI0_SIMO. MI(0) refers to the first bit input and MI(n) refers to the last bit input on SPI0_SOMI.

128

Peripheral Information and Electrical Specifications Copyright © 20082010, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Link(s): TMS320C6745/6747

TMS320C6745/6747

www. ti. com SPRS377D SEPTEMBER 2008 REVISED AUGUST 2010

Table 6-55. General Timing Requirements for SPI0 Slave Modes (1)

No. 9 10 11 tc(SPC)S tw(SPCH)S tw(SPCL)S PARAMATER Cycle Time, SPI0_CLK, All Slave Modes Pulse Width High, SPI0_CLK, All Slave Modes Pulse Width Low, SPI0_CLK, All Slave Modes Polarity = 0, Phase = 0, to SPI0_CLK rising Setup time, transmit data written to SPI before initial clock edge from master. (2) (3) Polarity = 0, Phase = 1, to SPI0_CLK rising Polarity = 1, Phase = 0, to SPI0_CLK falling Polarity = 1, Phase = 1, to SPI0_CLK falling Polarity = 0, Phase = 0, from SPI0_CLK rising Delay, subsequent bits valid on SPI0_SOMI after transmit edge of SPI0_CLK Polarity = 0, Phase = 1, from SPI0_CLK falling Polarity = 1, Phase = 0, from SPI0_CLK falling Polarity = 1, Phase = 1, from SPI0_CLK rising Polarity = 0, Phase = 0, from SPI0_CLK falling Output hold time, SPI0_SOMI valid after receive edge of SPI0_CLK Polarity = 0, Phase = 1, from SPI0_CLK rising Polarity = 1, Phase = 0, from SPI0_CLK rising Polarity = 1, Phase = 1, from SPI0_CLK falling Polarity = 0, Phase = 0, to SPI0_CLK falling Input Setup Time, SPI0_SIMO valid before receive edge of SPI0_CLK Polarity = 0, Phase = 1, to SPI0_CLK rising Polarity = 1, Phase = 0, to SPI0_CLK rising Polarity = 1, Phase = 1, to SPI0_CLK falling Polarity = 0, Phase = 0, from SPI0_CLK falling Input Hold Time, SPI0_SIMO valid after receive edge of SPI0_CLK Polarity = 0, Phase = 1, from SPI0_CLK rising Polarity = 1, Phase = 0, from SPI0_CLK rising Polarity = 1, Phase = 1, from SPI0_CLK falling (1) (2) (3) 0. 5tc(SPC)S -3 0. 5tc(SPC)S -3 ns 0. 5tc(SPC)S -3 0. 5tc(SPC)S -3 0 0 ns 0 0 5 5 ns 5 5 MIN greater of 3P or 20 ns 18 18 2P 2P ns 2P 2P 18. 5 18. 5 ns MAX UNIT ns ns ns

12

tsu(SOMI_SPC)S

13

td(SPC_SOMI)S

18. 5

14

toh(SPC_SOMI)S

15

tsu(SIMO_SPC)S

16

tih(SPC_SIMO)S

P = SYSCLK2 period First bit may be MSB or LSB depending upon SPI configuration. SO(0) refers to first bit and SO(n) refers to last bit output on SPI0_SOMI. SI(0) refers to the first bit input and SI(n) refers to the last bit input on SPI0_SIMO. Measured from the termination of the write of new data to the SPI module, In analyzing throughput requirements, additional internal bus cycles must be accounted for to allow data to be written to the SPI module by the DSP CPU.

Copyright © 20082010, Texas Instruments Incorporated

Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): TMS320C6745/6747

129

ADVANCE INFORMATION

18. 5

TMS320C6745/6747

SPRS377D SEPTEMBER 2008 REVISED AUGUST 2010 www. ti. com (3)

Table 6-56. Additional (1) SPI0 Master Timings, 4-Pin Enable Option (2)

No. PARAMATER Polarity = 0, Phase = 0, to SPI0_CLK rising Delay from slave assertion of SPI0_ENA active to first SPI0_CLK from master. (4) Polarity = 0, Phase = 1, to SPI0_CLK rising Polarity = 1, Phase = 0, to SPI0_CLK falling Polarity = 1, Phase = 1, to SPI0_CLK falling Polarity = 0, Phase = 0, from SPI0_CLK falling Max delay for slave to deassert SPI0_ENA after final SPI0_CLK edge to ensure master does not begin the next transfer. (5) Polarity = 0, Phase = 1, from SPI0_CLK falling Polarity = 1, Phase = 0, from SPI0_CLK rising Polarity = 1, Phase = 1, from SPI0_CLK rising (1) (2) (3) (4) (5) MIN

MAX 3P + 3 0. 5tc(SPC)M + 3P + 3

UNIT

17

td(ENA_SPC)M

ns 3P + 3 0. 5tc(SPC)M + 3P + 3 0. 5tc(SPC)M + P + 5 P+5 ns 0. 5tc(SPC)M + P + 5 P+5

18

td(SPC_ENA)M

These parameters are in addition to the general timings for SPI master modes (Table 6-54). [. . . ] All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. [. . . ]