Detailed instructions for use are in the User's Guide.

[. . . ] TMS320DM365

www. ti. com SPRS457D MARCH 2009 REVISED NOVEMBER 2010

TMS320DM365 Digital Media System-on-Chip (DMSoC)

Check for Samples: TMS320DM365

1 TMS320DM365 Digital Media System-on-Chip (DMSoC)

1. 1

12

Features

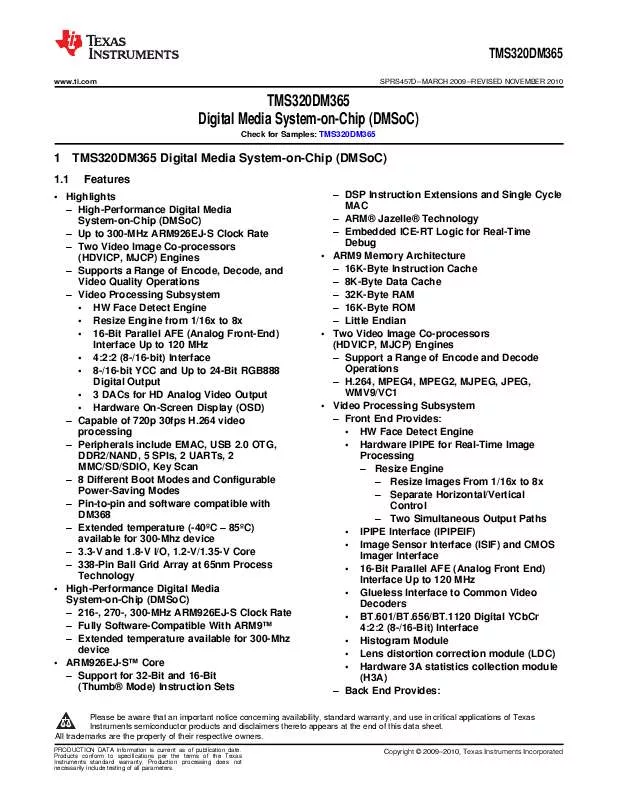

DSP Instruction Extensions and Single Cycle MAC ARM® Jazelle® Technology Embedded ICE-RT Logic for Real-Time Debug · ARM9 Memory Architecture 16K-Byte Instruction Cache 8K-Byte Data Cache 32K-Byte RAM 16K-Byte ROM Little Endian · Two Video Image Co-processors (HDVICP, MJCP) Engines Support a Range of Encode and Decode Operations H. 264, MPEG4, MPEG2, MJPEG, JPEG, WMV9/VC1 · Video Processing Subsystem Front End Provides: · HW Face Detect Engine · Hardware IPIPE for Real-Time Image Processing Resize Engine Resize Images From 1/16x to 8x Separate Horizontal/Vertical Control Two Simultaneous Output Paths · IPIPE Interface (IPIPEIF) · Image Sensor Interface (ISIF) and CMOS Imager Interface · 16-Bit Parallel AFE (Analog Front End) Interface Up to 120 MHz · Glueless Interface to Common Video Decoders · BT. 601/BT. 656/BT. 1120 Digital YCbCr 4:2:2 (8-/16-Bit) Interface · Histogram Module · Lens distortion correction module (LDC) · Hardware 3A statistics collection module (H3A) Back End Provides:

· Highlights High-Performance Digital Media System-on-Chip (DMSoC) Up to 300-MHz ARM926EJ-S Clock Rate Two Video Image Co-processors (HDVICP, MJCP) Engines Supports a Range of Encode, Decode, and Video Quality Operations Video Processing Subsystem · HW Face Detect Engine · Resize Engine from 1/16x to 8x · 16-Bit Parallel AFE (Analog Front-End) Interface Up to 120 MHz · 4:2:2 (8-/16-bit) Interface · 8-/16-bit YCC and Up to 24-Bit RGB888 Digital Output · 3 DACs for HD Analog Video Output · Hardware On-Screen Display (OSD) Capable of 720p 30fps H. 264 video processing Peripherals include EMAC, USB 2. 0 OTG, DDR2/NAND, 5 SPIs, 2 UARTs, 2 MMC/SD/SDIO, Key Scan 8 Different Boot Modes and Configurable Power-Saving Modes Pin-to-pin and software compatible with DM368 Extended temperature (-40ºC 85ºC) available for 300-Mhz device 3. 3-V and 1. 8-V I/O, 1. 2-V/1. 35-V Core 338-Pin Ball Grid Array at 65nm Process Technology · High-Performance Digital Media System-on-Chip (DMSoC) 216-, 270-, 300-MHz ARM926EJ-S Clock Rate Fully Software-Compatible With ARM9TM Extended temperature available for 300-Mhz device · ARM926EJ-STM Core Support for 32-Bit and 16-Bit (Thumb® Mode) Instruction Sets

1

2

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

Copyright © 20092010, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

TMS320DM365

SPRS457D MARCH 2009 REVISED NOVEMBER 2010 www. ti. com

· ·

· ·

· · ·

·

· ·

·

Hardware On-Screen Display (OSD) Composite NTSC/PAL video encoder output · 8-/16-bit YCC and Up to 24-Bit RGB888 Digital Output · 3 DACs for HD Analog Video Output · LCD Controller · BT. 601/BT. 656 Digital YCbCr 4:2:2 (8-/16-Bit) Interface Analog-to-Digital Convertor (ADC) Power Management and Real Time Clock Subsystem (PRTCSS) Real Time Clock 16-Bit Host-Port Interface (HPI) 10/100 Mb/s Ethernet Media Access Controller (EMAC) - Digital Media IEEE 802. 3 Compliant Supports Media Independent Interface (MII) Management Data I/O (MDIO) Module Key Scan Voice Codec External Memory Interfaces (EMIFs) DDR2 and mDDR SDRAM 16-bit wide EMIF With 256 MByte Address Space (1. 8-V I/O) Asynchronous16-/8-bit Wide EMIF (AEMIF) · Flash Memory Interfaces NAND (8-/16-bit Wide Data) 16 MB NOR Flash, SRAM OneNAND(16-bit Wide Data) Flash Card Interfaces Two Multimedia Card (MMC) / Secure Digital (SD/SDIO) SmartMedia/xD Enhanced Direct-Memory-Access (EDMA) Controller (64 Independent Channels) USB Port with Integrated 2. 0 High-Speed PHY that Supports USB 2. 0 High-Speed Device USB 2. 0 High-Speed Host (mini-host, supporting one external device) USB On The Go (HS-USB OTG) Four 64-Bit General-Purpose Timers (each configurable as two 32-bit timers)

· ·

· One 64-Bit Watch Dog Timer · Two UARTs (One fast UART with RTS and CTS Flow Control) · Five Serial Port Interfaces (SPI) each with two Chip-Selects · One Master/Slave Inter-Integrated Circuit (I2C) BusTM · One Multi-Channel Buffered Serial Port (McBSP) I2S AC97 Audio Codec Interface S/PDIF via Software Standard Voice Codec Interface (AIC12) SPI Protocol (Master Mode Only) Direct Interface to T1/E1 Framers Time Division Multiplexed Mode (TDM) 128 Channel Mode · Four Pulse Width Modulator (PWM) Outputs · Four RTO (Real Time Out) Outputs · Up to 104 General-Purpose I/O (GPIO) Pins (Multiplexed with Other Device Functions) · Boot Modes On-Chip ARM ROM Bootloader (RBL) to Boot From NAND Flash, MMC/SD, UART, USB, SPI, EMAC, or HPI AEMIF (NOR and OneNAND) · Configurable Power-Saving Modes · Crystal or External Clock Input (typically 19. 2 Mhz, 24 MHz, 27 Mhz or 36 MHz) · Flexible PLL Clock Generators · Debug Interface Support IEEE-1149. 1 (JTAGTM) Boundary-Scan-Compatible ETB (Embedded Trace Buffer) with 4K-Bytes Trace Buffer memory Device Revision ID Readable by ARM · 338-Pin Ball Grid Array (BGA) Package (ZCE Suffix), 0. 65-mm Ball Pitch · 65nm Process Technology · 3. 3-V and 1. 8-V I/O, 1. 2-V/ 1. 35-V Internal · Community Resources TI E2E Community TI Embedded Processors Wiki

2

TMS320DM365 Digital Media System-on-Chip (DMSoC) Copyright © 20092010, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Link(s): TMS320DM365

TMS320DM365

www. ti. com SPRS457D MARCH 2009 REVISED NOVEMBER 2010

1. 2

Description

Developers can now deliver pixel-perfect images at up to 720p H. 264 at 30fps in their digital video designs without concerns of video format support, constrained network bandwidth, limited system storage capacity or cost with the new TMS320DM365 digital media processor based on DaVinci technology from Texas Instruments Incorporated (TI). [. . . ] The device has three output clock pins (CLKOUT[3:1]). See Section 3. 3 for more information on CLKOUT[3:1]. Note: Please ensure that the appropriate oscillator input pin (GIO81/OSCCFG) frequency range setting is set correctly. For more details on this pin setting, see Section 3. 7. 6.

6. 6. 1

MXI1 Oscillator

The MXI1 (typically 24 MHz, can also be 19. 2 MHz, 27 MHz, or 36 MHz) oscillator provides the primary reference clock for the device. The on-chip oscillator requires an external crystal connected across the MXI1 and MXO1 pins, along with two load capacitors, as shown in Figure 6-5. The external crystal load capacitors must be connected only to the oscillator ground pin (VSS_MX1). Also, the PLL power pin (VDDA_PLL1) should be connected to the power supply through a ferrite bead, L1 in the example circuit shown in Figure 6-5. Note: If an external oscillator is to be used, the external oscillator clock signal should be connected to the MXI1 pin with a 1. 8V amplitude. The MXO1 should be left unconnected and the VSS_MX1 signal should be connected to board ground (Vss).

MXI1/CLKIN

MXO1

VSS_MX1

VDDA_PLL1

VSSA_PLL1 0. 1 µF

Crystal 19. 2 MHz 24 MHz or 36 MHz C1 C2 L1

0. 1 µF

Figure 6-5. MXI1 Oscillator The load capacitors, C1 and C2, should be chosen such that the equation is satisfied (typical values are C1 = C2 = 10 pF). CL in the equation is the load specified by the crystal manufacturer. All discrete components used to implement the oscillator circuit should be placed as close as possible to the associated oscillator pins (MXI1 and MXO1) and to the VSS_MX1 pin.

CL C 1C2 (C1 C2)

Copyright © 20092010, Texas Instruments Incorporated

Peripheral Information and Electrical Specifications Submit Documentation Feedback Product Folder Link(s): TMS320DM365

81

TMS320DM365

SPRS457D MARCH 2009 REVISED NOVEMBER 2010 www. ti. com

Table 6-3. Switching Characteristics Over Recommended Operating Conditions for System Oscillator

PARAMETER Start-up time (from power up until oscillating at stable frequency) Oscillation frequency Crystal ESR Frequency stability 19 - 30 MHz 30 - 36 MHz 19. 2/24/2 7/36 60 40 +/-50 MIN TYP MAX 2 UNIT ms MHz ppm

6. 6. 2

Clock PLL Electrical Data/Timing (Input and Output Clocks)

Table 6-4. Timing Requirements for MXI1/CLKIN1 (1)

(2) (3)

(see Figure 6-6)

DEVICE MIN TYP MAX 52. 083 0. 55C 0. 55C . 05C . 02C UNIT ns ns ns ns ns

NO . 1 2 3 4 5 (1) (2) (3) tc(MXI1) tw(MXI1H) tw(MXI1L) tt(MXI1) tJ(MXI1) Cycle time, MXI1/CLKIN1 Pulse duration, MXI1/CLKIN1 high Pulse duration, MXI1/CLKIN1 low Transition time, MXI1/CLKIN1 Period jitter, MXI1/CLKIN1

27. 7 0. 45C 0. 45C

The reference points for the rise and fall transitions are measured at VIL MAX and VIH MIN. For example, when MXI1/CLKIN1 frequency is 24 MHz use C = 41. 6 ns. tc(MXI1) = 52. 083 ns, tc(MXI1) = 41. 6 ns, tc(MXI1) = 37. 037 ns, and tc(MXI1) = 27. 7 ns are the only supported cycle times for MXI1/CLKIN1.

5 2 1 4

MXI1/CLKIN 3 4

Figure 6-6. MXI1/CLKIN1 Timing

82

Peripheral Information and Electrical Specifications Copyright © 20092010, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Link(s): TMS320DM365

TMS320DM365

www. ti. com SPRS457D MARCH 2009 REVISED NOVEMBER 2010

Table 6-5. Switching Characteristics Over Recommended Operating Conditions for CLKOUT0/CLKOUT1 (1) (2) (see Figure 6-7)

NO. 1 2 3 4 5 6 (1) (2) tC(CLKOUT0/CLKOUT1) tw(CLKOUT0H/CLKOUT1H) tw(CLKOUT0L/CLKOUT1L) tt(CLKOUT0/CLKOUT1) td(MXI1H-CLKOUT0H/CLKOUT1H) td(MXI1L-CLKOUT0L/CLKOUT1L) PARAMETER Cycle time, CLKOUT0/CLKOUT1 Pulse duration, CLKOUT0/CLKOUT1 high Pulse duration, CLKOUT0/CLKOUT1 low Transition time, CLKOUT0/CLKOUT1 Delay time, MXI1/CLKIN1 high to CLKOUT0/CLKOUT1 high Delay time, MXI1/CLKIN1I low to CLKOUT0/CLKOUT1 low 1 1 DEVICE MIN 27. 7 . 45P . 45P . 55P . 55P 3 8 8 TYP MAX UNIT ns ns ns ns ns ns

The reference points for the rise and fall transitions are measured at VOL MAX and VOHMIN. P = 1/CLKOUT0/1 clock frequency in nanoseconds (ns). For example, when CLKOUT1 frequency is 24 MHz use P = 41. 6 ns.

5 MXI1/CLKIN 6

2 1 CLKOUT0/1 3

4

4

Figure 6-7. [. . . ] All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. [. . . ]