User manual TEXAS INSTRUMENTS TMS320F28033 DATA MANUAL REV D

Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets... DON'T FORGET : ALWAYS READ THE USER GUIDE BEFORE BUYING !!!

If this document matches the user guide, instructions manual or user manual, feature sets, schematics you are looking for, download it now. Lastmanuals provides you a fast and easy access to the user manual TEXAS INSTRUMENTS TMS320F28033. We hope that this TEXAS INSTRUMENTS TMS320F28033 user guide will be useful to you.

Lastmanuals help download the user guide TEXAS INSTRUMENTS TMS320F28033.

Manual abstract: user guide TEXAS INSTRUMENTS TMS320F28033DATA MANUAL REV D

Detailed instructions for use are in the User's Guide.

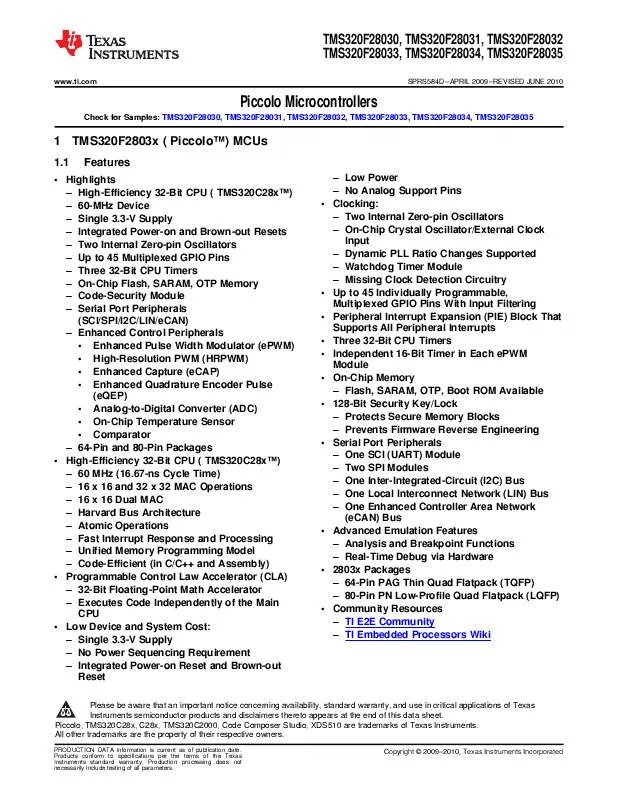

[. . . ] TMS320F28030, TMS320F28031, TMS320F28032 TMS320F28033, TMS320F28034, TMS320F28035

www. ti. com SPRS584D APRIL 2009 REVISED JUNE 2010

Piccolo Microcontrollers

Check for Samples: TMS320F28030, TMS320F28031, TMS320F28032, TMS320F28033, TMS320F28034, TMS320F28035

1 TMS320F2803x ( PiccoloTM) MCUs

1. 1

123

Features

Low Power No Analog Support Pins Clocking: Two Internal Zero-pin Oscillators On-Chip Crystal Oscillator/External Clock Input Dynamic PLL Ratio Changes Supported Watchdog Timer Module Missing Clock Detection Circuitry Up to 45 Individually Programmable, Multiplexed GPIO Pins With Input Filtering Peripheral Interrupt Expansion (PIE) Block That Supports All Peripheral Interrupts Three 32-Bit CPU Timers Independent 16-Bit Timer in Each ePWM Module On-Chip Memory Flash, SARAM, OTP, Boot ROM Available 128-Bit Security Key/Lock Protects Secure Memory Blocks Prevents Firmware Reverse Engineering Serial Port Peripherals One SCI (UART) Module Two SPI Modules One Inter-Integrated-Circuit (I2C) Bus One Local Interconnect Network (LIN) Bus One Enhanced Controller Area Network (eCAN) Bus Advanced Emulation Features Analysis and Breakpoint Functions Real-Time Debug via Hardware 2803x Packages 64-Pin PAG Thin Quad Flatpack (TQFP) 80-Pin PN Low-Profile Quad Flatpack (LQFP) Community Resources TI E2E Community TI Embedded Processors Wiki

· Highlights High-Efficiency 32-Bit CPU ( TMS320C28xTM) 60-MHz Device Single 3. 3-V Supply Integrated Power-on and Brown-out Resets Two Internal Zero-pin Oscillators Up to 45 Multiplexed GPIO Pins Three 32-Bit CPU Timers On-Chip Flash, SARAM, OTP Memory Code-Security Module Serial Port Peripherals (SCI/SPI/I2C/LIN/eCAN) Enhanced Control Peripherals · Enhanced Pulse Width Modulator (ePWM) · High-Resolution PWM (HRPWM) · Enhanced Capture (eCAP) · Enhanced Quadrature Encoder Pulse (eQEP) · Analog-to-Digital Converter (ADC) · On-Chip Temperature Sensor · Comparator 64-Pin and 80-Pin Packages · High-Efficiency 32-Bit CPU ( TMS320C28xTM) 60 MHz (16. 67-ns Cycle Time) 16 x 16 and 32 x 32 MAC Operations 16 x 16 Dual MAC Harvard Bus Architecture Atomic Operations Fast Interrupt Response and Processing Unified Memory Programming Model Code-Efficient (in C/C++ and Assembly) · Programmable Control Law Accelerator (CLA) 32-Bit Floating-Point Math Accelerator Executes Code Independently of the Main CPU · Low Device and System Cost: Single 3. 3-V Supply No Power Sequencing Requirement Integrated Power-on Reset and Brown-out Reset

1

·

· · · · · ·

·

·

·

·

2

3

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. Piccolo, TMS320C28x, C28x, TMS320C2000, Code Composer Studio, XDS510 are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

Copyright © 20092010, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. [. . . ] The start address of each task is specified by the MVECT registers. No limit on task size as long as the tasks fit within the CLA program memory space. One task is serviced at a time through to completion. Upon task completion, a task-specific interrupt is flagged within the PIE. When a task finishes, the next highest-priority pending task is automatically started. · Task trigger mechanisms: C28x CPU via the IACK instruction Task1 to Task7: the corresponding ADC or ePWM module interrupt. For example: · Task1: ADCINT1 or EPWM1_INT · Task2: ADCINT2 or EPWM2_INT · Task7: ADCINT7 or EPWM7_INT Task8: ADCINT8 or by CPU Timer 0. · Memory and Shared Peripherals: Two dedicated message RAMs for communication between the CLA and the main CPU. The C28x CPU can map CLA program and data memory to the main CPU space or CLA space. The CLA has direct access to the ADC Result registers, comparator registers, and the ePWM+HRPWM registers.

Copyright © 20092010, Texas Instruments Incorporated

Peripherals Submit Documentation Feedback Product Folder Link(s): TMS320F28030 TMS320F28031 TMS320F28032 TMS320F28033 TMS320F28034 TMS320F28035

47

TMS320F28030, TMS320F28031, TMS320F28032 TMS320F28033, TMS320F28034, TMS320F28035

SPRS584D APRIL 2009 REVISED JUNE 2010 www. ti. com

IACK Peripheral Interrupts ADCINT1 to ADCINT8 EPWM1_INT to EPWM8_INT INT CPU Timer 0 MPERINT1 to MPERINT8

CLA Control Registers

MIFR MIOVF MICLR MICLROVF MIFRC MIER MIRUN MPISRCSEL1 MVECT1 MVECT2 MVECT3 MVECT4 MVECT5 MVECT6 MVECT7 MVECT8 MMEMCFG MCTL Map to CLA or CPU Space CLA_INT1 to CLA_INT8 PIE LVF LUF INT11 INT12 Main 28x CPU

Main CPU Read/Write Data Bus

CLA Program Address Bus

CLA Program Memory

CLA Program Data Bus

Map to CLA or CPU Space

Main CPU BUS

SYSCLKOUT CLAENCLK SYSRS

CLA Shared Message RAMs

CLA Data Bus

CLA Execution Registers

MPC(12) MSTF(32) MR0(32) MR1(32) MR2(32) MR3(32) MAR0(32) MAR1(32)

MEALLOW

CLA Data Read Address Bus CLA Data Read Data Bus CLA Data Write Address Bus CLA Data Write Data Bus

ADC Result Registers ePWM and HRPWM Registers Comparator Registers

Main CPU Read Data Bus

Figure 4-1. CLA Block Diagram

48

Peripherals

Copyright © 20092010, Texas Instruments Incorporated

Submit Documentation Feedback Product Folder Link(s): TMS320F28030 TMS320F28031 TMS320F28032 TMS320F28033 TMS320F28034 TMS320F28035

Main CPU Bus

CLA Data Memory

TMS320F28030, TMS320F28031, TMS320F28032 TMS320F28033, TMS320F28034, TMS320F28035

www. ti. com SPRS584D APRIL 2009 REVISED JUNE 2010

Table 4-1. CLA Control Registers

REGISTER NAME MVECT1 MVECT2 MVECT3 MVECT4 MVECT5 MVECT6 MVECT7 MVECT8 MCTL MMEMCFG MPISRCSEL1 MIFR MIOVF MIFRC MICLR MICLROVF MIER MIRUN MIPCTL MPC (2) MAR0 (2) MAR1

(2)

CLA1 ADDRESS 0x1400 0x1401 0x1402 0x1403 0x1404 0x1405 0x1406 0x1407 0x1410 0x1411 0x1414 0x1420 0x1421 0x1422 0x1423 0x1424 0x1425 0x1426 0x1427 0x1428 0x142A 0x142B 0x142E 0x1430 0x1434 0x1438 0x143C

SIZE (x16) 1 1 1 1 1 1 1 1 1 1 2 1 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2

EALLOW PROTECTED Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes

DESCRIPTION (1) CLA Interrupt/Task 1 Start Address CLA Interrupt/Task 2 Start Address CLA Interrupt/Task 3 Start Address CLA Interrupt/Task 4 Start Address CLA Interrupt/Task 5 Start Address CLA Interrupt/Task 6 Start Address CLA Interrupt/Task 7 Start Address CLA Interrupt/Task 8 Start Address CLA Control Register CLA Memory Configure Register Peripheral Interrupt Source Select Register 1 Interrupt Flag Register Interrupt Overflow Register Interrupt Force Register Interrupt Clear Register Interrupt Overflow Clear Register Interrupt Enable Register Interrupt RUN Register Interrupt Priority Control Register CLA Program Counter CLA Aux Register 0 CLA Aux Register 1 CLA STF Register CLA R0H Register CLA R1H Register CLA R2H Register CLA R3H Register

MSTF (2) MR0 (2) MR1

(2)

MR2 (2) MR3 (2) (1) (2)

All registers in this table are CSM protected The main C28x CPU has read only access to this register for debug purposes. The main CPU cannot perform CPU or debugger writes to this register.

Table 4-2. CLA Message RAM

ADDRESS RANGE 0x1480 0x14FF 0x1500 0x157F SIZE (x16) 128 128 DESCRIPTION CLA to CPU Message RAM CPU to CLA Message RAM

Copyright © 20092010, Texas Instruments Incorporated

Peripherals Submit Documentation Feedback Product Folder Link(s): TMS320F28030 TMS320F28031 TMS320F28032 TMS320F28033 TMS320F28034 TMS320F28035

49

TMS320F28030, TMS320F28031, TMS320F28032 TMS320F28033, TMS320F28034, TMS320F28035

SPRS584D APRIL 2009 REVISED JUNE 2010 www. ti. com

4. 2

Analog Block

A 12-bit ADC core is implemented that has different timings than the 12-bit ADC used on F280x/F2833x. The ADC wrapper is modified to incorporate the new timings and also other enhancements to improve the timing control of start of conversions. Figure 4-2 shows the interaction of the analog module with the rest of the F2803x system.

64-Pin VDDA 80-Pin VDDA (3. 3 V) VDDA (Agnd) VSSA VREFLO Interface Reference Diff VREFHI A0 B0 A1 B1 A2 COMP1OUT AIO2 AIO10 10-Bit DAC Comp1

VREFLO VSSA Tied To VSSA VREFLO VREFHI VREFHI Tied To A0 A0 A1 A2 A3 A4 A6 A7 B0 B1 B2 B3 B4 B6 B7 A1 A2 A3 A4 A6 A7 B0 B1 B2 B3 B4 B5 B6 B7 A5

Simultaneous Sampling Channels

B2 A3 B3 A4 B4

ADC COMP2OUT AIO4 AIO12 10-Bit DAC Comp2

B5 Temperature Sensor A5 A6 B6 A7 B7 COMP3OUT AIO6 AIO14 10-Bit DAC Comp3

Signal Pinout

Figure 4-2. Analog Pin Configurations

50

Peripherals

Copyright © 20092010, Texas Instruments Incorporated

Submit Documentation Feedback Product Folder Link(s): TMS320F28030 TMS320F28031 TMS320F28032 TMS320F28033 TMS320F28034 TMS320F28035

TMS320F28030, TMS320F28031, TMS320F28032 TMS320F28033, TMS320F28034, TMS320F28035

www. ti. com SPRS584D APRIL 2009 REVISED JUNE 2010

4. 2. 1

4. 2. 1. 1

ADC

Features

The core of the ADC contains a single 12-bit converter fed by two sample-and-hold circuits. The sample-and-hold circuits can be sampled simultaneously or sequentially. These, in turn, are fed by a total of up to 16 analog input channels. The converter can be configured to run with an internal bandgap reference to create true-voltage based conversions or with a pair of external voltage references (VREFHI/VREFLO) to create ratiometric-based conversions. Contrary to previous ADC types, this ADC is not sequencer-based. It is easy for the user to create a series of conversions from a single trigger. [. . . ] All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. [. . . ]

DISCLAIMER TO DOWNLOAD THE USER GUIDE TEXAS INSTRUMENTS TMS320F28033 Lastmanuals offers a socially driven service of sharing, storing and searching manuals related to use of hardware and software : user guide, owner's manual, quick start guide, technical datasheets...manual TEXAS INSTRUMENTS TMS320F28033